2.3.6. Analog PMA Settings Parameters

In older device families, such as Arria® 10 and Stratix® V, you can only set the analog PMA settings through the Assignment Editor or the Quartus Settings File (QSF). However, for Stratix® 10 transceivers, you can also set them through the Native PHY IP Parameter Editor. There is also an option to provide sample QSF assignments for the settings chosen through the Native PHY IP Parameter Editor. Use this method when you need to modify one or two individual settings, or want to modify the settings without regenerating the IP.

You can specify values for the following types of analog PMA settings parameters in the Native PHY IP Parameter Editor:

- TX analog PMA settings:

- TX PMA analog mode rules

- Output swing level (VOD)

- Use default TX PMA analog settings

- Pre-emphasis first pre-tap polarity

- Pre-emphasis first pre-tap magnitude

- Pre-emphasis first post-tap polarity

- Pre-emphasis first post-tap magnitude

- Slew rate control

- On-chip termination

- High-speed compensation

- RX analog PMA settings:

- Use default RX PMA analog settings

- RX on-chip termination

- RX adaptation mode

- CTLE AC Gain

- CTLE EQ Gain

- VGA DC Gain

- Start PMA DFE adaptation auto

The following settings can not be set through the Native PHY IP Parameter Editor. You must set these through the Quartus® Prime Pro Edition Assignment Editor:

- REFCLK I/O Standard

- REFCLK Termination

- TX serial pin I/O Standard

- RX serial pin I/O Standard

To improve performance, Stratix® 10 FPGAs use a High Speed Differential I/O. Select High Speed Differential I/O as the I/O standard for the Stratix® 10 transmitter and receiver pins in the Quartus® Prime Pro Edition Assignment Editor or Quartus Settings File (.qsf). The pin assignments in the .qsf always take precedence over the settings selected in the Native PHY IP Parameter Editor.

The syntax is as follows:

set_instance_assignment -name IO_STANDARD "HIGH SPEED DIFFERENTIAL I/O" -to <serial TX/RX pin name> -entity <name of the top-level file>

Refer to the Dedicated Reference Clock Settings section for details on the I/O standard and termination settings for the dedicated reference clock.

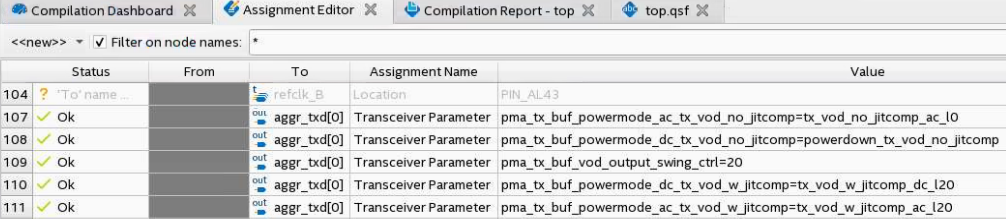

- Ok means that the assignment is recognized; thus, the Quartus® Prime Pro Edition fitter compilation uses the assignment.

- ? means that the assignment is not recognized; thus, the Quartus® Prime Pro Edition fitter compilation ignores the assignment.

| Parameter | Value | Description |

|---|---|---|

| TX PMA analog mode rules | User Selection (cei_11100_lr to xfp_9950) | Selects the analog protocol mode to pre-select the TX pin swing settings (VOD, Pre-emphasis, and slew rate). After loading the pre-selected values in the GUI, if one or more of the individual TX pin swing settings need to be changed, then select the Provide sample QSF assignments option to modify the settings through the QSF. |

| Use default TX PMA analog settings | On/Off | Selects whether to use default or custom TX PMA analog settings. |

| Output Swing Level (VOD) | 17 to 31 | Selects the transmitter programmable output differential voltage swing. (Use the Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator to see how changing VOD affects your signal.)

Note: Although the GUI displays a range of 0-31, you must not select values lower than 17.

Note: The Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator was created for the ES device family only. For L- and H-Tile Stratix® 10 production devices, you must use the L-Tile/H-Tile Transceiver Native PHY Stratix® 10 FPGA IP to verify the valid output swing level (VOD), pre-emphasis pre-tap and post tap settings under the Analog PMA Settings tab in the IP GUI. An invalid setting generates error messages under the System Messages pane.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_vod_output_swing_ctrl=<value>" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_ac_tx_vod_no_jitcomp = TX_VOD_NO_JITCOMP_AC_L0" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_dc_tx_vod_no_jitcomp = powerdown_tx_vod_no_jitcomp" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_ac_tx_vod_w_jitcomp = TX_VOD_W_JITCOMP_AC_L20" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_dc_tx_vod_w_jitcomp= TX_VOD_W_JITCOMP_DC_L20" -to <serial TX pin name>

Note: For powerdown_tx_vod_no_jitcomp, if the reference clock is paused or not available during operation, both TX buffer positive and negative pins are equal to the TX output common mode voltage (VOCM). For the VOCM value, refer to the Stratix® 10 Device Data Sheet.

|

| Pre-Emphasis First Pre-Tap Polarity | neg (-) pos (+) |

Selects the polarity of the first pre-tap for pre-emphasis. (Use the Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator to see how changing pre-emphasis affects your signal.)

Note: The Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator was created for the ES device family only. For L- and H-Tile Stratix® 10 production devices, you must use the L-Tile/H-Tile Transceiver Native PHY Stratix® 10 FPGA IP to verify the valid output swing level (VOD), pre-emphasis pre-tap and post tap settings under the Analog PMA Settings tab in the IP GUI. An invalid setting generates error messages under the System Messages pane.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_pre_emp_sign_pre_tap_1t=fir_pre_1t_<value>" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_ac_pre_tap = TX_PRE_TAP_AC_ON" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_dc_pre_tap = TX_PRE_TAP_DC_ON" -to <serial TX pin name> |

| Pre-Emphasis First Pre-Tap Magnitude | 0 to 15 (0 to -6 dB gain for positive sign, and 0 to 6 dB gain for negative sign) | Selects the magnitude of the first pre-tap for pre-emphasis. (Use the Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator to see how changing pre-emphasis affects your signal.)

Note: The Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator was created for the ES device family only. For L- and H-Tile Stratix® 10 production devices, you must use the L-Tile/H-Tile Transceiver Native PHY Stratix® 10 FPGA IP to verify the valid output swing level (VOD), pre-emphasis pre-tap and post tap settings under the Analog PMA Settings tab in the IP GUI. An invalid setting generates error messages under the System Messages pane.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_pre_emp_switching_ctrl_pre_tap_1t=<value>" -to <serial TX pin name> |

| Pre-Emphasis First Post-Tap Polarity | neg (-) pos (+) |

Selects the polarity of the first post-tap for pre-emphasis. (Use the Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator to see how changing pre-emphasis affects your signal.)

Note: The Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator was created for the ES device family only. For L- and H-Tile Stratix® 10 production devices, you must use the L-Tile/H-Tile Transceiver Native PHY Stratix® 10 FPGA IP to verify the valid output swing level (VOD), pre-emphasis pre-tap and post tap settings under the Analog PMA Settings tab in the IP GUI. An invalid setting generates error messages under the System Messages pane.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_pre_emp_sign_1st_post_tap=fir_post_1t_<value>" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_compensation_posttap_en=enable" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_compensation_en=enable" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_ac_post_tap = TX_POST_TAP_W_JITCOMP_AC_ON" -to <serial TX pin name> set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_powermode_dc_post_tap = TX_POST_TAP_W_JITCOMP_DC_ON" -to <serial TX pin name> |

| Pre-Emphasis First Post -Tap Magnitude | 0 to 24 (0 to -14 dB gain for positive sign, and 0 to 14 dB gain for negative sign) | Selects the magnitude of the first post-tap for pre-emphasis. (Use the Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator to see how changing pre-emphasis affects your signal.)

Note: The Stratix® 10 L-Tile/H-Tile Pre-emphasis and Output Swing Estimator was created for the ES device family only. For L- and H-Tile Stratix® 10 production devices, you must use the L-Tile/H-Tile Transceiver Native PHY Stratix® 10 FPGA IP to verify the valid output swing level (VOD), pre-emphasis pre-tap and post tap settings under the Analog PMA Settings tab in the IP GUI. An invalid setting generates error messages under the System Messages pane.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_pre_emp_switching_ctrl_1st_post_tap=<value>" -to <serial TX pin name> |

| Slew Rate Control | 0 (slowest) - 5 (fastest) | Selects the slew rate of the TX output signal. Valid values span from slowest to the fastest rate. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_slew_rate_ctrl=slew_r<value>" -to <serial TX pin name> |

| On-Chip Termination |

|

Selects the on-chip TX differential termination according to the on-board trace impedance at the TX output pin. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_term_sel=<value>" -to <serial TX pin name> |

| High Speed Compensation | enable/disable | Enables the power-distribution network (PDN) induced inter-symbol interference (ISI) compensation in the TX driver. When enabled, it reduces the PDN- induced ISI jitter, but increases the power consumption. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_tx_buf_compensation_en=<value>" -to <serial TX pin name> disable is only for PCIe* Gen1 and Gen2 mode. Refer to the "Parameters for the Native PHY IP Core in PIPE Gen1, Gen2, Gen3 Modes - Analog PMA Settings" table for details. |

| Parameter | Value | Description |

|---|---|---|

| RX PMA analog mode rules | User Selection (analog_off to user_custom) | Selects the analog protocol mode rules to pre-select the RX pin swing settings (VOD, Pre-emphasis, and Slew Rate). |

| Use default RX PMA analog settings | On/Off | Selects whether to use default or custom RX PMA analog settings.

Note: When you disable this setting by selecting Off, you should select one of the available options in the Native PHY IP Parameter Editor as the PMA analog settings.

|

| RX adaptation mode |

|

Select manual CTLE if you intend to tune the analog front end of all the transceiver channels by sweeping combinations of the TX and RX EQ parameters together. Select one of the adaptive modes based on your system loss characteristics if you intend to use the Adaptation engine in the RX PMA. Only use ctle_dfe_mode_2 for PCIe Gen3. When using any of the adaptive modes, refer to the PMA Functions section for more information about how to reconfigure across modes, and how to start and stop adaptation. |

| RX On-chip Termination | Supported:

Unsupported:

|

Specifies the on-chip termination value for the receiver according to the on-board trace impedance at the RX input pin.

Note: To set RX On-chip Termination to OFF, either select r_hiz value in the Transceiver Native PHY IP parameter editor or use direct write via Avalon® memory-mapped interface. Refer to RX Termination for the register address. Quartus® Prime software version 21.3 and later support r_hiz option in the Transceiver Native PHY IP parameter editor. Quartus® Prime software version 21.2 and later support r_hiz option in the .qsf syntax to override the option in the Transceiver Native PHY IP parameter editor.

Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_rx_buf_term_sel=<value>" -to <serial RX pin name> |

| CTLE AC Gain | 0 to 15 (-2 dB at the peak to +10 dB at the peak) | Specifies the CTLE broadband gain. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_rx_buf_ctle_ac_gain=<value>" -to <serial RX pin name> |

| CTLE EQ Gain | 0 to 47 (0 dB to 16 dB) | Specifies the CTLE equalization setting. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_rx_buf_ctle_eq_gain=<value>" -to <serial RX pin name> |

| VGA DC Gain | 0 to 31 ( -5 dB to +7 dB) | Specifies the VGA Gain for the receiver. Syntax: set_instance_assignment -name HSSI_PARAMETER "pma_rx_buf_vga_dc_gain=<value>" -to <serial RX pin name> |

| Start PMA DFE adaptation auto | On/Off | Specifies to start the RX PMA DFE adaptation automatically when a RX link reset is detected. The IP detects the de-assertion of rx_digitalreset and kick start the adaptation engine automatically. This includes after device power-up, after a full user reset sequence or after a user triggered RX link reset. To enable this feature, you must disable the Use default RX PMA analog settings, and select the Adaptive CTLE, Adaptive VGA, 1-Tap Adaptive DFE or Adaptive CTLE, Adaptive VGA, All-Tap Adaptive DFE mode. When Adaptive CTLE, Adaptive VGA, 1-Tap Adaptive DFE is selected, only the DFE tap #1, #2 and #3 get adapted. When Adaptive CTLE, Adaptive VGA, All-Tap Adaptive DFE is selected, all DFE taps get adapted. |

| Parameter | Value | Description |

|---|---|---|

| Provide sample QSF assignments | On/Off | Selects the option to provide QSF assignments to the above configuration, in case one or more individual values need to change. The sample QSF assignments list has different sets of attributes depending on the enabled blocks in the currently-selected analog PMA settings. |