17.14. Transceiver Reconfiguration Controller PLL Reconfiguration

The PLL registers for dynamic reconfiguration feature are available when you select one of the following transceiver PHY IP cores:

- Custom PHY IP Core

- Low Latency PHY IP Core

- Deterministic Latency PHY IP Core

- Arria V, Arria V GZ, Cyclone V, and Stratix V Native PHYs

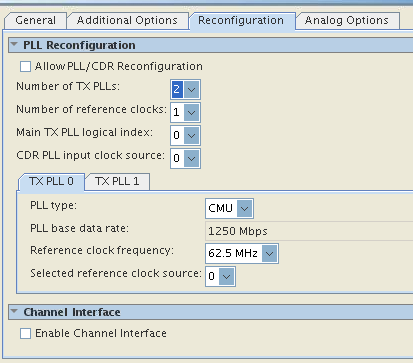

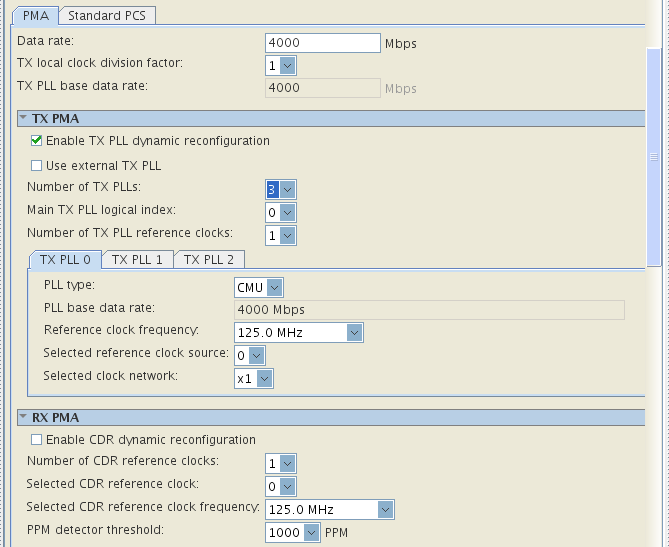

You can establish the number of possible PLL configurations on the Reconfiguration tab of the appropriate transceiver PHY IP core. The Reconfiguration tab allows you to specify up to five input reference clocks and up to four TX PLLs. You can also change the input clock source to the CDR PLL; up to five input clock sources are possible. If you plan to dynamically reconfigure the PLLs in your design, you must also enable Allow PLL Reconfiguration and specify the Main TX PLL logical index which is the PLL that the Intel® Quartus® Prime software instantiates at power up. The following figures illustrates these parameters.

For more information about the Stratix V reset sequence, refer to Transceiver Reset Control in Stratix V Devices in volume 2 of the Stratix V Device Handbook. For Arria V devices, refer to Transceiver Reset Control and Power-Down in Arria V Devices. For Cyclone V devices refer to Transceiver Reset Control and Power Down in Cyclone V Devices.

When you specify multiple PLLs, you must use the QSF assignment, XCVR_TX_PLL_RECONFIG_GROUP, to identify the PLLs within a reconfiguration group using the Assignment Editor. The XCVR_TX_PLL_RECONFIG_GROUP assignment identifies PLLs that the Intel® Quartus® Prime Fitter can merge. You can assign TX PLLs from different transceiver PHY IP core instances to the same group.