External Memory Interface Handbook Volume 2: Design Guidelines: For UniPHY-based Device Families

ID

683385

Date

3/06/2023

Public

1. Planning Pin and FPGA Resources

2. DDR2 and DDR3 SDRAM Board Design Guidelines

3. Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines

4. LPDDR2 SDRAM Board Design Guidelines

5. RLDRAM II and RLDRAM 3 Board Design Guidelines

6. QDR II/II+ SRAM Board Design Guidelines

7. Implementing and Parameterizing Memory IP

8. Simulating Memory IP

9. Analyzing Timing of Memory IP

10. Debugging Memory IP

11. Optimizing the Controller

12. PHY Considerations

13. Power Estimation Methods for External Memory Interfaces

1.1.1. Estimating Pin Requirements

1.1.2. DDR, DDR2, and DDR3 SDRAM Clock Signals

1.1.3. DDR, DDR2, and DDR3 SDRAM Command and Address Signals

1.1.4. DDR, DDR2, and DDR3 SDRAM Data, Data Strobes, DM/DBI, and Optional ECC Signals

1.1.5. DDR, DDR2, and DDR3 SDRAM DIMM Options

1.1.6. QDR II and QDR II+ SRAM Clock Signals

1.1.7. QDR II and QDR II+ SRAM Command Signals

1.1.8. QDR II and QDR II+ SRAM Address Signals

1.1.9. QDR II and QDR II+ SRAM Data, BWS, and QVLD Signals

1.1.10. RLDRAM II and RLDRAM 3 Clock Signals

1.1.11. RLDRAM II and RLDRAM 3 Commands and Addresses

1.1.12. RLDRAM II and RLDRAM 3 Data, DM and QVLD Signals

1.1.13. LPDDR2 Clock Signal

1.1.14. LPDDR2 Command and Address Signal

1.1.15. LPDDR2 Data, Data Strobe, and DM Signals

1.1.16. Maximum Number of Interfaces

1.1.17. OCT Support

1.1.16.1. Maximum Number of DDR SDRAM Interfaces Supported per FPGA

1.1.16.2. Maximum Number of DDR2 SDRAM Interfaces Supported per FPGA

1.1.16.3. Maximum Number of DDR3 SDRAM Interfaces Supported per FPGA

1.1.16.4. Maximum Number of QDR II and QDR II+ SRAM Interfaces Supported per FPGA

1.1.16.5. Maximum Number of RLDRAM II Interfaces Supported per FPGA

1.1.16.6. Maximum Number of LPDDR2 SDRAM Interfaces Supported per FPGA

1.2.1. General Pin-out Guidelines for UniPHY-based External Memory Interface IP

1.2.2. Pin-out Rule Exceptions for ×36 Emulated QDR II and QDR II+ SRAM Interfaces in Arria II, Stratix III and Stratix IV Devices

1.2.3. Pin-out Rule Exceptions for RLDRAM II and RLDRAM 3 Interfaces

1.2.4. Pin-out Rule Exceptions for QDR II and QDR II+ SRAM Burst-length-of-two Interfaces

1.2.5. Pin Connection Guidelines Tables

1.2.6. PLLs and Clock Networks

1.2.5.1. DDR3 SDRAM With Leveling Interface Pin Utilization Applicable for Arria V GZ, Stratix III, Stratix IV, and Stratix V Devices

1.2.5.2. QDR II and QDR II+ SRAM Pin Utilization for Arria II, Arria V, Stratix III, Stratix IV, and Stratix V Devices

1.2.5.3. RLDRAM II CIO Pin Utilization for Arria II GZ, Arria V, Stratix III, Stratix IV, and Stratix V Devices

1.2.5.4. LPDDR2 Pin Utilization for Arria V, Cyclone V, and MAX 10 FPGA Devices

1.2.5.5. Additional Guidelines for Arria V GZ and Stratix V Devices

1.2.5.6. Additional Guidelines for Arria V ( Except Arria V GZ) Devices

1.2.5.7. Additional Guidelines for MAX 10 Devices

1.2.5.8. Additional Guidelines for Cyclone V Devices

1.2.6.1. Number of PLLs Available in Intel® Device Families

1.2.6.2. Number of Enhanced PLL Clock Outputs and Dedicated Clock Outputs Available in Intel® Device Families

1.2.6.3. Number of Clock Networks Available in Intel® Device Families

1.2.6.4. Clock Network Usage in UniPHY-based Memory Interfaces—DDR2 and DDR3 SDRAM (1) (2)

1.2.6.5. Clock Network Usage in UniPHY-based Memory Interfaces—RLDRAM II, and QDR II and QDR II+ SRAM

1.2.6.6. PLL Usage for DDR, DDR2, and DDR3 SDRAM Without Leveling Interfaces

1.2.6.7. PLL Usage for DDR3 SDRAM With Leveling Interfaces

2.1. Leveling and Dynamic Termination

2.2. DDR2 Terminations and Guidelines

2.3. DDR3 Terminations in Arria V, Cyclone V, Stratix III, Stratix IV, and Stratix V

2.4. Layout Approach

2.5. Channel Signal Integrity Measurement

2.6. Design Layout Guidelines

2.7. Package Deskew

2.8. Document Revision History

3.2.1. Overview of ODT Control

3.2.2. DIMM Configuration

3.2.3. Dual-DIMM Memory Interface with Slot 1 Populated

3.2.4. Dual-DIMM with Slot 2 Populated

3.2.5. Dual-DIMM Memory Interface with Both Slot 1 and Slot 2 Populated

3.2.6. Dual-DIMM DDR2 Clock, Address, and Command Termination and Topology

3.2.7. Control Group Signals

3.2.8. Clock Group Signals

7.2.1.1. DDR2 SDRAM Controller with UniPHY Intel FPGA IP Interfaces

7.2.1.2. DDR3 SDRAM Controller with UniPHY Intel FPGA IP Interfaces

7.2.1.3. LPDDR2 SDRAM Controller with UniPHY Intel FPGA IP Interfaces

7.2.1.4. QDR II and QDR II+ SRAM Controller with UniPHY Intel FPGA IP Interfaces

7.2.1.5. RLDRAM II Controller with UniPHY Intel FPGA IP Interfaces

7.2.1.6. RLDRAM 3 UniPHY Intel FPGA IP Interface

7.2.3.1. PHY Settings for UniPHY IP

7.2.3.2. Memory Parameters for LPDDR2, DDR2 and DDR3 SDRAM Controller with UniPHY Intel FPGA IP

7.2.3.3. Memory Parameters for QDR II and QDR II+ SRAM Controller with UniPHY Intel FPGA IP

7.2.3.4. Memory Parameters for RLDRAM II Controller with UniPHY Intel FPGA IP

7.2.3.5. Memory Timing Parameters for DDR2, DDR3, and LPDDR2 SDRAM Controller with UniPHY Intel FPGA IP

7.2.3.6. Memory Timing Parameters for QDR II and QDR II+ SRAM Controller with UniPHY Intel FPGA IP

7.2.3.7. Memory Timing Parameters for RLDRAM II Controller with UniPHY Intel FPGA IP

7.2.3.8. Memory Parameters for RLDRAM 3 UniPHY Intel FPGA IP

8.2.1. Simulation Scripts

8.2.2. Preparing the Vendor Memory Model

8.2.3. Functional Simulation with Verilog HDL

8.2.4. Functional Simulation with VHDL

8.2.5. Simulating the Example Design

8.2.6. UniPHY Abstract PHY Simulation

8.2.7. PHY-Only Simulation

8.2.8. Post-fit Functional Simulation

8.2.9. Simulation Issues

9.1. Memory Interface Timing Components

9.2. FPGA Timing Paths

9.3. Timing Constraint and Report Files for UniPHY IP

9.4. Timing Analysis Description

9.5. Timing Report DDR

9.6. Report SDC

9.7. Calibration Effect in Timing Analysis

9.8. Timing Model Assumptions and Design Rules

9.9. Common Timing Closure Issues

9.10. Optimizing Timing

9.11. Timing Deration Methodology for Multiple Chip Select DDR2 and DDR3 SDRAM Designs

9.12. Performing I/O Timing Analysis

9.13. Document Revision History

9.4.1.1. Address and Command

9.4.1.2. PHY or Core

9.4.1.3. PHY or Core Reset

9.4.1.4. Read Capture and Write

9.4.1.5. Read Resynchronization

9.4.1.6. DQS versus CK—Arria II GX and Cyclone IV Devices

9.4.1.7. Write Leveling tDQSS

9.4.1.8. Write Leveling tDSH/tDSS

9.4.1.9. DK versus CK (RLDRAM II with UniPHY)

9.4.1.10. Bus Turnaround Time

9.9.1. Missing Timing Margin Report

9.9.2. Incomplete Timing Margin Report

9.9.3. Read Capture Timing

9.9.4. Write Timing

9.9.5. Address and Command Timing

9.9.6. PHY Reset Recovery and Removal

9.9.7. Clock-to-Strobe (for DDR and DDR2 SDRAM Only)

9.9.8. Read Resynchronization and Write Leveling Timing (for SDRAM Only)

10.1. Resource and Planning Issues

10.2. Interface Configuration Performance Issues

10.3. Functional Issue Evaluation

10.4. Timing Issue Characteristics

10.5. Verifying Memory IP Using the Signal Tap II Logic Analyzer

10.6. Hardware Debugging Guidelines

10.7. Categorizing Hardware Issues

10.8. EMIF Debug Toolkit Overview

10.9. Document Revision History

10.3.1. Correct Combination of the Quartus Prime Software and ModelSim* - Intel® FPGA Edition Device Models

10.3.2. Intel® IP Memory Model

10.3.3. Vendor Memory Model

10.3.4. Insufficient Memory in Your PC

10.3.5. Transcript Window Messages

10.3.6. Passing Simulation

10.3.7. Modifying the Example Driver to Replicate the Failure

10.6.1. Create a Simplified Design that Demonstrates the Same Issue

10.6.2. Measure Power Distribution Network

10.6.3. Measure Signal Integrity and Setup and Hold Margin

10.6.4. Vary Voltage

10.6.5. Use Freezer Spray and Heat Gun

10.6.6. Operate at a Lower Speed

10.6.7. Determine Whether the Issue Exists in Previous Versions of Software

10.6.8. Determine Whether the Issue Exists in the Current Version of Software

10.6.9. Try A Different PCB

10.6.10. Try Other Configurations

10.6.11. Debugging Checklist

11.2.1. DDR2 SDRAM Controller

11.2.2. Auto-Precharge Commands

11.2.3. Additive Latency

11.2.4. Bank Interleaving

11.2.5. Command Queue Look-Ahead Depth

11.2.6. Additive Latency and Bank Interleaving

11.2.7. User-Controlled Refresh

11.2.8. Frequency of Operation

11.2.9. Burst Length

11.2.10. Series of Reads or Writes

11.2.11. Data Reordering

11.2.12. Starvation Control

11.2.13. Command Reordering

11.2.14. Bandwidth

11.2.15. Efficiency Monitor

7.4.9.4. Equations for RLDRAM 3 Board Skew Parameters

| Parameter | Description/Equation |

|---|---|

| Maximum CK delay to device | The delay of the longest CK trace from the FPGA to any device.

|

| Maximum DK delay to device | The delay of the longest DK trace from the FPGA to any device.

|

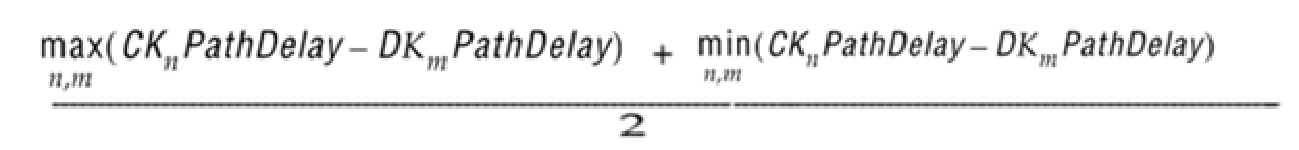

| Average delay difference between DK and CK | The average delay difference between the DK signals and the CK signal, calculated by averaging the longest and smallest DK delay minus the CK delay. Positive values represent DK signals that are longer than CK signals and negative values represent DK signals that are shorter than CK signals. The Quartus Prime software uses this skew to optimize the delay of the DK signals to have appropriate setup and hold margins.

|

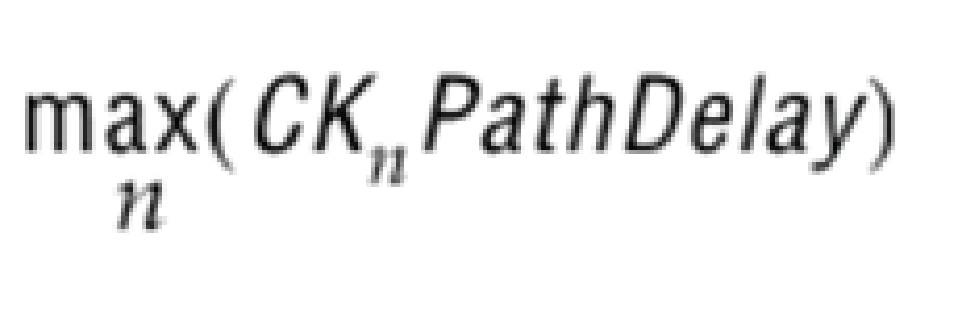

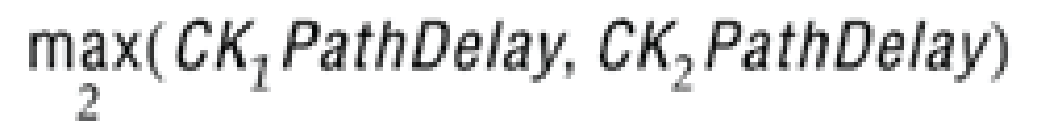

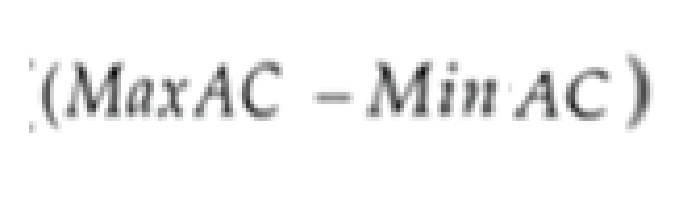

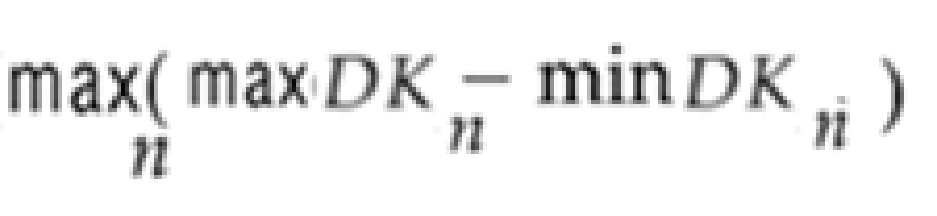

| Maximum system skew within address/command bus |

|

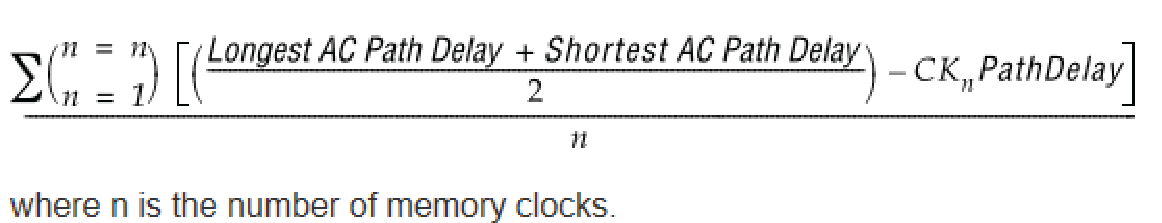

| Average delay difference between address/command and CK | The average delay difference between the address and command signals and the CK signal, calculated by averaging the longest and smallest Address/Command signal delay minus the CK delay. Positive values represent address and command signals that are longer than CK signals and negative values represent address and command signals that are shorter than CK signals. The Quartus Prime software uses this skew to optimize the delay of the address and command signals to have appropriate setup and hold margins.

|

| Maximum board skew within QK group | The largest skew between all DQ and DM pins in a QK group. Enter your board skew only. Package skew will be calculated automatically, based on the memory interface configuration, and added to this value. This value affects the read capture and write margins.

|

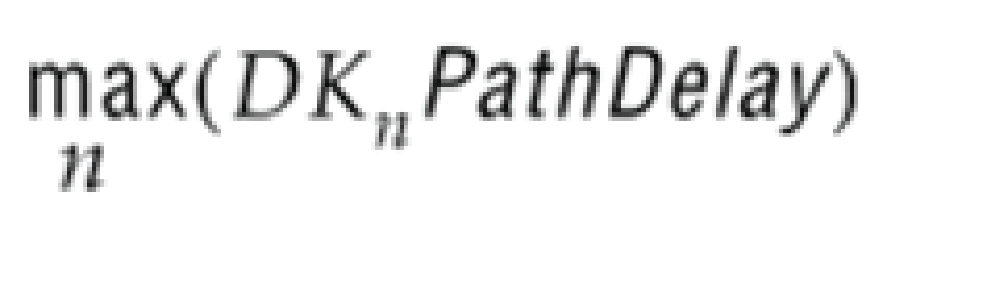

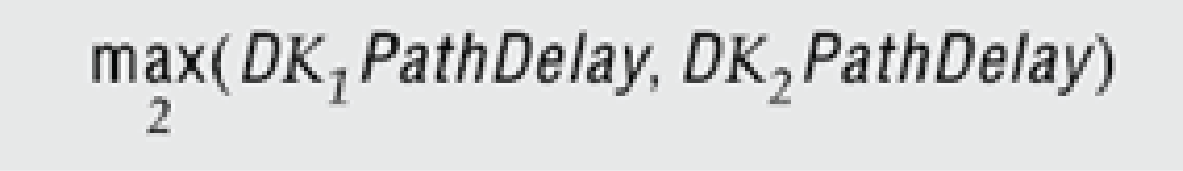

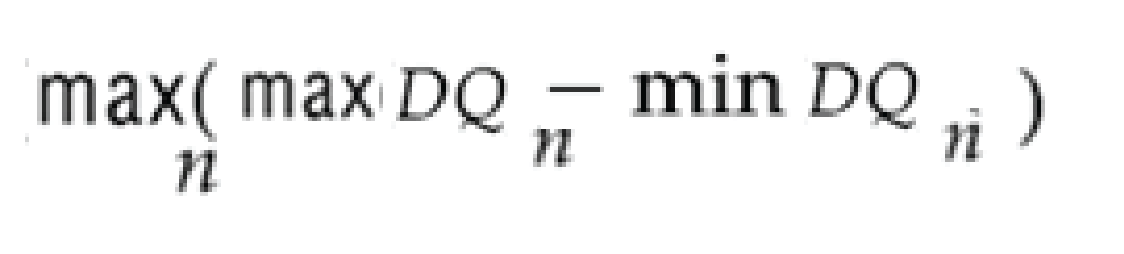

| Maximum skew between DK groups | The largest skew between DK signals in different DK groups.

|