Visible to Intel only — GUID: dsu1461013342091

Ixiasoft

Product Discontinuance Notification

1. About the RapidIO II Intel® FPGA IP

2. Getting Started

3. Parameter Settings

4. Functional Description

5. Signals

6. Software Interface

7. Testbench

8. RapidIO II IP Core User Guide Archives

9. Document Revision History for the RapidIO II Intel® FPGA IP User Guide

A. Initialization Sequence

B. Differences Between RapidIO II IP Core and RapidIO IP Core

2.1. Installing and Licensing Intel® FPGA IP Cores

2.2. Intel® FPGA IP Evaluation Mode

2.32.4. Generating IP Cores2.32.4. Generating IP Cores

2.32.4. Generating IP Cores2.32.4. Generating IP Cores

2.5. RapidIO II IP Core Testbench Files

2.6. Simulating IP Cores

2.7. Integrating Your IP Core in Your Design

2.8. Compiling the Full Design and Programming the FPGA

2.9. Instantiating Multiple RapidIO II IP Cores in V-series FPGA devices

3.4.1. Device Identity CAR

3.4.2. Device Information CAR

3.4.3. Assembly Identity CAR

3.4.4. Assembly Information CAR

3.4.5. Processing Element Features CAR

3.4.6. Switch Port Information CAR

3.4.7. Switch Route Table Destination ID Limit CAR

3.4.8. Data Streaming Information CAR

3.4.9. Source Operations CAR

3.4.10. Destination Operations CAR

4.3.3.1. Maintenance Interface Transactions

4.3.3.2. Maintenance Interface Signals

4.3.3.3. Initiating MAINTENANCE Read and Write Transactions

4.3.3.4. Defining the Maintenance Address Translation Windows

4.3.3.5. Responding to MAINTENANCE Read and Write Requests

4.3.3.6. Handling Port-Write Transactions

4.3.3.7. Maintenance Interface Transaction Examples

4.3.3.8. Maintenance Packet Error Handling

4.3.5.3.1. User Sending Write Request

4.3.5.3.2. User Receiving Write Request

4.3.5.3.3. User Sending Read Request and Receiving Read Response

4.3.5.3.4. User Receiving Read Request and Sending Read Response

4.3.5.3.5. User Sending Streaming Write Request

4.3.5.3.6. User Receiving Streaming Write Request

6.1.1. CAR Memory Map

6.1.2. CSR Memory Map

6.1.3. LP-Serial Extended Features Block Memory Map

6.1.4. LP-Serial Lane Extended Features Block Memory Map

6.1.5. Error Management Extensions Extended Features Block Memory Map

6.1.6. Maintenance Module Registers Memory Map

6.1.7. I/O Logical Layer Master Module Registers Memory Map

6.1.8. I/O Logical Layer Slave Module Registers Memory Map

6.1.9. Doorbell Module Registers Memory Map

6.2.1.1. LP-Serial Register Block Header

6.2.1.2. Port Link Time-out Control CSR

6.2.1.3. Port Response Time-out Control CSR

6.2.1.4. Port General Control CSR

6.2.1.5. Port 0 Link Maintenance Request CSR

6.2.1.6. Port 0 Link Maintenance Response CSR

6.2.1.7. Port 0 Local AckID CSR

6.2.1.8. Port 0 Control 2 CSR

6.2.1.9. Port 0 Error and Status CSR

6.2.1.10. Port 0 Control CSR

6.3.1.1. CAR Memory Map

6.3.1.2. Device Identity CAR

6.3.1.3. Device Information CAR

6.3.1.4. Assembly Identity CAR

6.3.1.5. Assembly Information CAR

6.3.1.6. Processing Element Features CAR

6.3.1.7. Switch Port Information CAR

6.3.1.8. Source Operations CAR

6.3.1.9. Destination Operations CAR

6.3.1.10. Switch Route Table Destination ID Limit CAR

6.3.1.11. Data Streaming Information CAR

6.3.2.1. CSR Memory Map

6.3.2.2. Data Streaming Logical Layer Control CSR

6.3.2.3. Processing Element Logical Layer Control CSR

6.3.2.4. Local Configuration Space Base Address 0 CSR

6.3.2.5. Local Configuration Space Base Address 1 CSR

6.3.2.6. Base Device ID CSR

6.3.2.7. Host Base Device ID Lock CSR

6.3.2.8. Component Tag CSR

6.3.6.1. Error Management Extensions Extended Features Block Memory Map

6.3.6.2. Error Management Extensions Block Header

6.3.6.3. Logical/Transport Layer Error Detect

6.3.6.4. Logical/Transport Layer Error Enable

6.3.6.5. Logical/Transport Layer Address Capture

6.3.6.6. Logical/Transport Layer Device ID Capture

6.3.6.7. Logical/Transport Layer Control Capture

6.3.6.8. Port-Write Target Device ID

6.3.6.9. Packet Time-to-Live

6.3.6.10. Port 0 Error Detect

6.3.6.11. Port 0 Error Rate Enable

6.3.6.12. Port 0 Attributes Capture

6.3.6.13. Port 0 Packet/Control Symbol Capture 0

6.3.6.14. Port 0 Packet Capture 1

6.3.6.15. Port 0 Packet Capture 2

6.3.6.16. Port 0 Packet Capture 3

6.3.6.17. Port 0 Error Rate

6.3.6.18. Port 0 Error Rate Threshold

7.2.1. Reset, Initialization, and Configuration

7.2.2. Maintenance Write and Read Transactions

7.2.3. SWRITE Transactions

7.2.4. NREAD Transactions

7.2.5. NWRITE_R Transactions

7.2.6. NWRITE Transactions

7.2.7. Doorbell Transactions

7.2.8. Port-Write Transactions

7.2.9. Transactions Across the AVST Pass-Through Interface

Visible to Intel only — GUID: dsu1461013342091

Ixiasoft

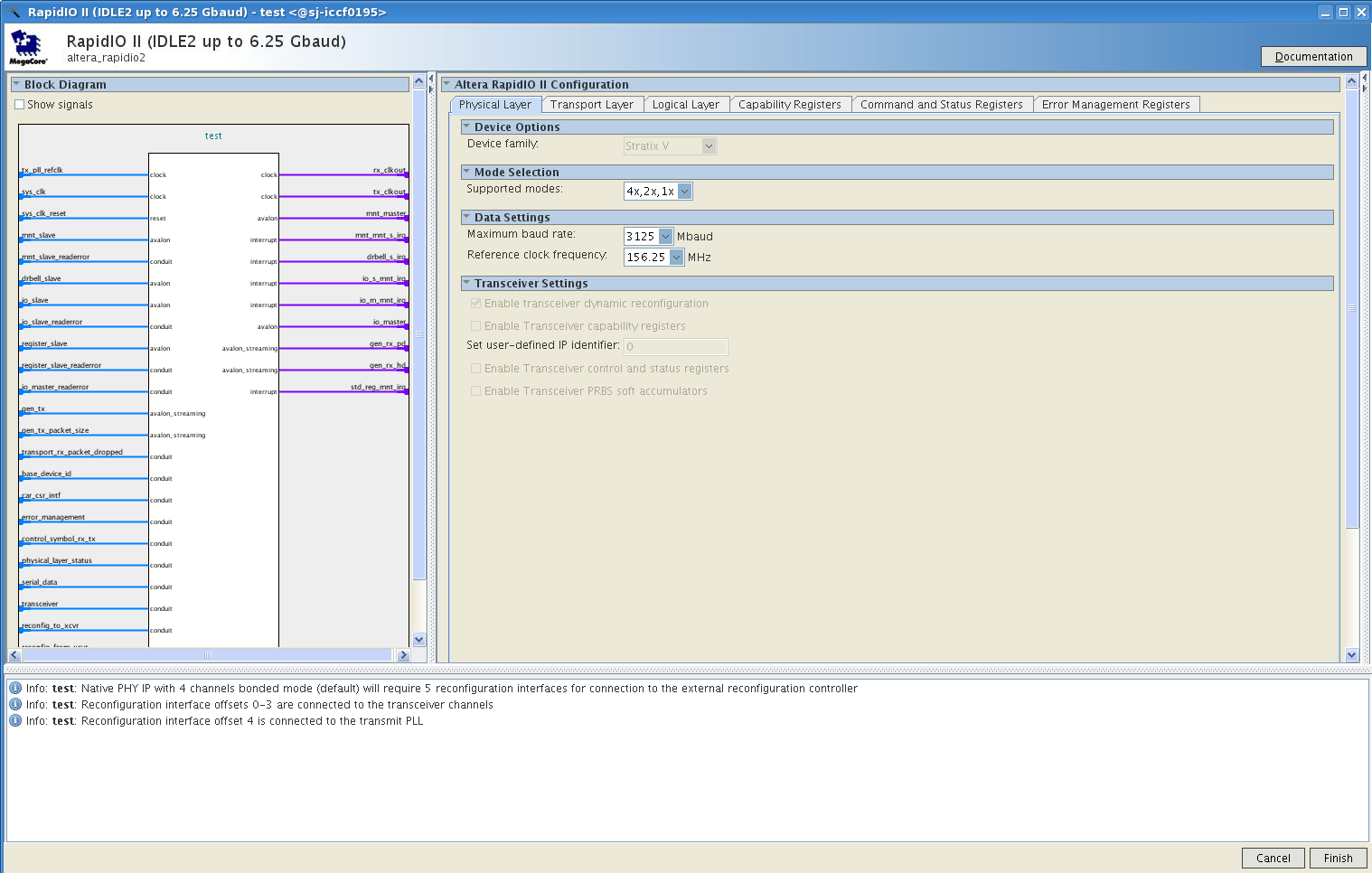

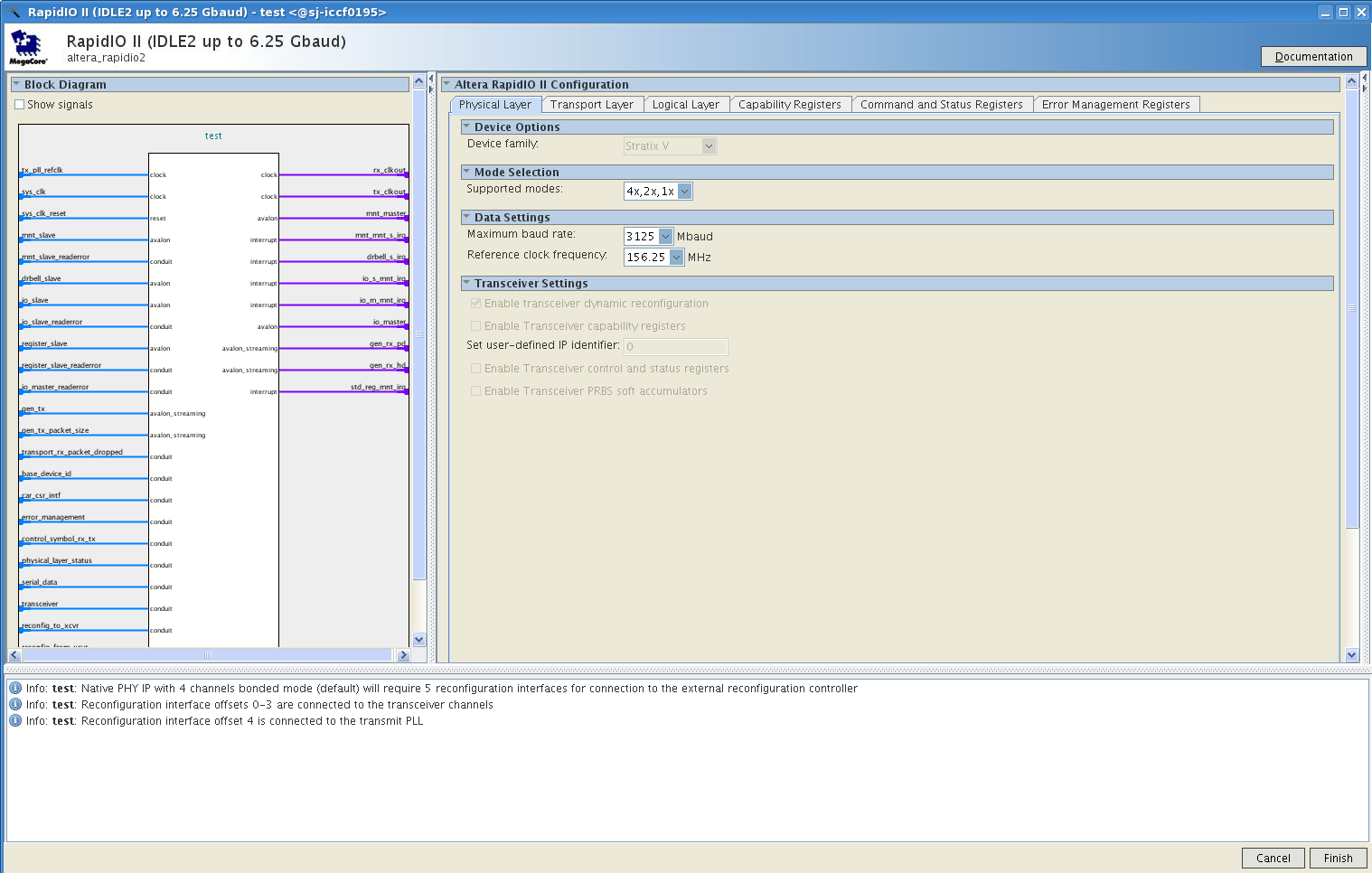

2.4. Generating IP Cores ( Intel® Quartus® Prime Standard Edition)

This topic describes parameterizing and generating an IP variation using a legacy parameter editor in the Intel® Quartus® Prime Standard Edition software. Some IP cores use a legacy version of the parameter editor for configuration and generation. Use the following steps to configure and generate an IP variation using a legacy parameter editor.

Legacy Parameter Editor

Note: The legacy parameter editor generates a different output file structure than the Intel® Quartus® Prime Pro Edition software.

- In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize. The parameter editor appears.

- Specify a top-level name and output HDL file type for your IP variation. This name identifies the IP core variation files in your project. Click OK. Do not include spaces in IP variation names or paths.

- Specify the parameters and options for your IP variation in the parameter editor. Refer to your IP core user guide for information about specific IP core parameters.

- Click Finish or Generate (depending on the parameter editor version). The parameter editor generates the files for your IP variation according to your specifications. Click Exit if prompted when generation is complete. The parameter editor adds the top-level .qip file to the current project automatically.

Note: For devices released prior to Intel® Arria® 10 devices, the generated .qip and .sip files must be added to your project to represent IP and Platform Designer systems. To manually add an IP variation generated with legacy parameter editor to a project, click Project > Add/Remove Files in Project and add the IP variation .qip file.Note: Some IP cores generate different HDL implementations according to the IP core parameters. The underlying RTL of these IP cores contains a unique code that prevents module name collisions between different variations of the IP core. This unique code remains consistent, given the same IP settings and software version during IP generation. This unique code can change if you edit the IP core's parameters or upgrade the IP core version. To avoid dependency on these unique codes in your simulation environment, refer to Generating a Combined Simulator Setup Script.

Related Information