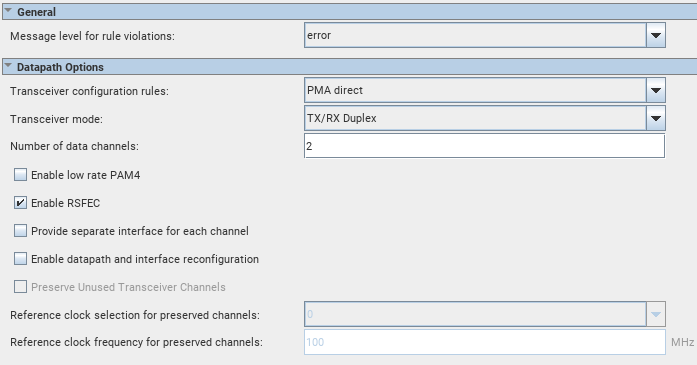

2.2.6. Reed Solomon Forward Error Correction (RS-FEC) Parameters

RS-FEC merging is not supported with more than one Native PHY IP instance. A Native PHY IP with an RS-FEC block enabled uses the whole RS-FEC block, even if it uses only one channel in the IP. You can use dynamic reconfiguration to utilize the same RS-FEC block for implementation on different protocols.

The RS-FEC IP core supports the following modes:

- 32GFC/ CPRI 24G (x1, x2, x3, x4)

- 128 GFC

- 25GE FEC Direct (x1, x2, x3, x4)

- 100 GbE

- Interlaken 7

| Supported Mode | RS-FEC Code Type | FEC Mode | Alignment/Scrambling/Transcoder Mode | Transcoder Bypass |

|---|---|---|---|---|

| 32GFC/ CPRI 24G (x1, x2, x3, x4) | NRZ (528, 514) | Fractured | Fibre channel | Not bypassed |

| 128 GFC | Aggregate | Fibre channel | Not bypassed | |

| 25GE FEC Direct (x1, x2, x3, x4) | Fractured | Basic | Not bypassed | |

| 100 GbE | Aggregate | Basic | Not bypassed | |

| Interlaken | PAM4 (544, 514) | Aggregate | Fibre channel | Bypassed |

| Parameter | Value | Description |

|---|---|---|

| Enable aggregate mode | On/Off | |

| RS-FEC Clocking Mode | EHIP clock Clock 0 Clock 1 Clock 2 Clock 3 No Clock |

Sets the clocking mode for the RS-FEC block. For some RS-FEC topologies, the clock selection is fixed. In all other cases, this control selects the TX adapter clock used to clock the RS-FEC block. |

| First RS-FEC Lane | first_lane0 first_lane1 first_lane2 first_lane3 |

Selects the first RS-FEC lane to be used. There are four lanes in the RS-FEC block. When the RS-FEC block is in fractured mode, any of the four lanes may be selected as the first lane. For multiple channel Native PHY IP core instances with the RS-FEC block enabled, the RS-FEC lanes used must be contiguous and must fit within a single four-channel RS-FEC block. |

| Alignment/Scrambling/Transcoder Mode | Basic Mode Fibre-Channel Mode |

Basic Mode selects Ethernet-like mode for a specific lane. The transcoder is not bypassed, alignment or codeword markers are used for alignment of the RS-FEC block, and the PN-5280 scrambling is disabled. Fibre-Channel Mode selects Fibre-Channel mode for RS-FEC lanes. Fibre-channel mode disables RS-FEC alignment/codeword markers. Selecting Fibre-Channel mode also selects PN-5280 scrambling when in fractured mode. CPRI Mode is identical to Fibre-Channel mode with respect to the RS-FEC operation. |

| Transcoder Bypass Lane | Not Bypassed Bypassed |

Selects the transcoder mode for RS-FEC lanes.

|