External Memory Interface Handbook Volume 3: Reference Material: For UniPHY-based Device Families

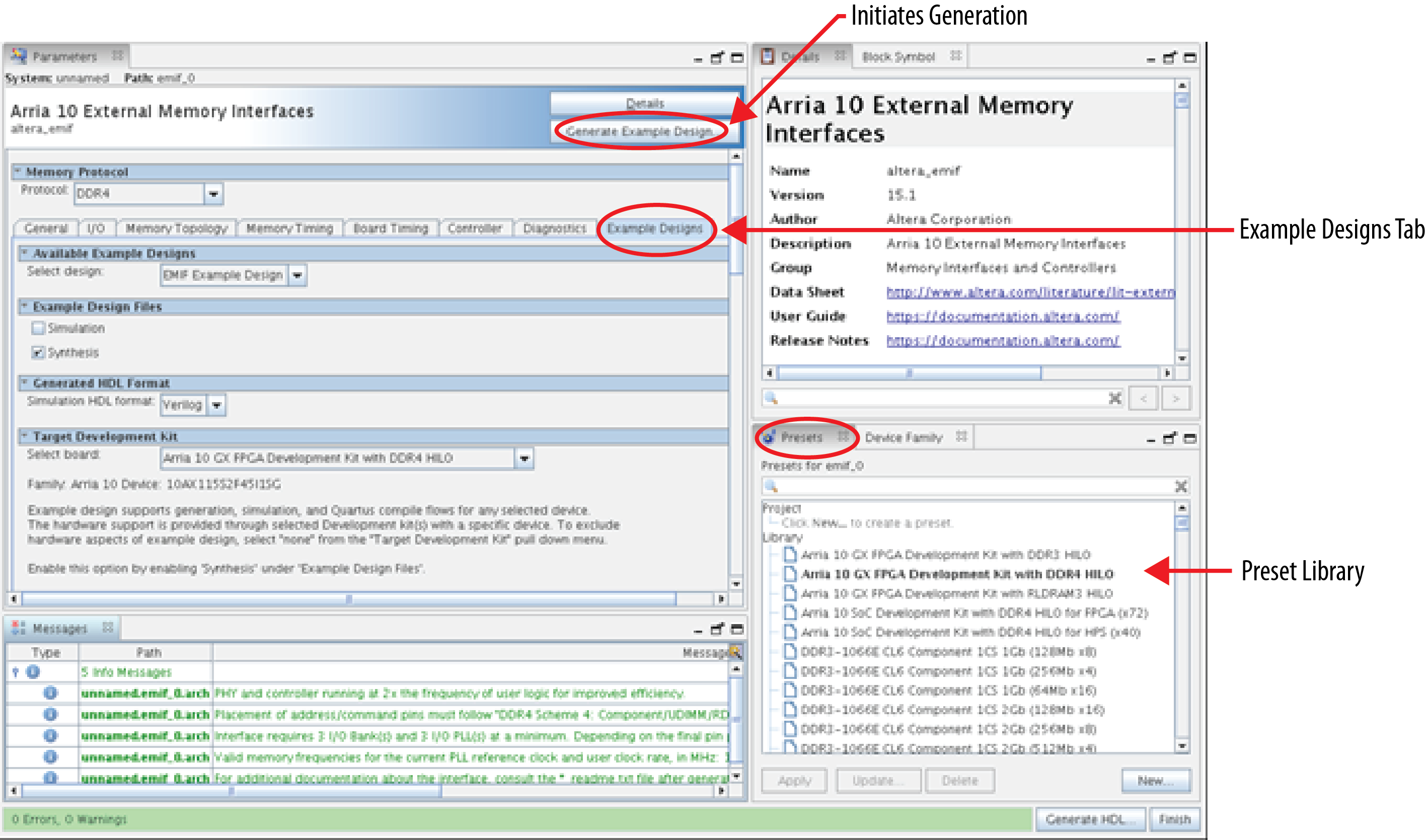

12.1.2. Example Designs Interface Tab

Available Example Designs Section

The Select design pulldown allows you to select the desired example design. At present, EMIF Example Design is the only available choice, and is selected by default.

Example Design Files Section

The example design supports generation, simulation, and Quartus Prime compilation flows for any selected device. The Simulation and Synthesis checkboxes in this section allow you to specify whether to generate a simulation file set, a synthesis file set, or both. Check Simulation to use the example design for simulation, or check Synthesis to use the example design for compilation and hardware. The system creates the specified file sets when you click the Generate Example Design button.

- To create a compilable project, you must run the quartus_sh -t make_qii_design.tcl script in the destination directory.

- To create a simulation project, you must run the quartus_sh -t make_sim_design.tcl script in the destination directory.

Generated HDL Format Section

The Simulation HDL format pulldown allows you to specify the target format for the generated design. At present, only Verilog filesets are supported.

Target Development Kit Section

The Select board pulldown in this section applies the appropriate development kit pin assignments to the example design.

- This setting is available only when you turn on the Synthesis checkbox in the Example Design Files section.

- This setting must match the applied development kit present, or else an error message appears.

If the value None appears in the Select board pulldown, it indicates that the current parameter selections do not match any development kit configurations. You may apply a development kit-specific IP and related parameter settings by selecting one of the presets from the preset library. When you apply a preset, the current IP and other parameter settings are set to match the selected preset. If you want to save your current settings, you should do so before you select a preset. If you do select a preset without saving your prior settings, you can always save the new preset settings under a different name

If you want to generate the example design for use on your own board, set Select board to None, generate the example design, and then add pin location constraints.