P-Tile Avalon® Memory-mapped Intel® FPGA IP for PCI Express* User Guide

4.10. Hard IP Reconfiguration Interface

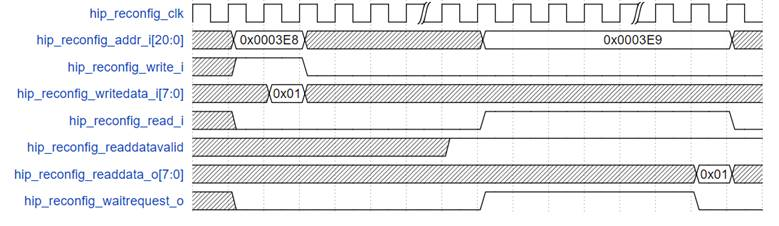

The Hard IP reconfiguration interface is an Avalon® -MM slave interface with a 21‑bit address and an 8‑bit data bus. It is also sometimes referred to as the User Avalon® -MM Interface. You can use this interface to dynamically modify the value of configuration registers. Note that after a warm reset or cold reset, changes made to the configuration registers of the Hard IP via the Hard IP reconfiguration interface are lost as these registers revert back to their default values.

In Root Port mode, the application logic uses the Hard IP reconfiguration interface to access its PCIe configuration space to perform link control functions (such as Hot Reset, link disable, or link retrain).

| Signal Name | Direction | Description | Clock Domain | EP/RP |

|---|---|---|---|---|

| hip_reconfig_clk | I | Reconfiguration clock 50 MHz - 125 MHz (Range) 100 MHz (Recommended) |

EP/RP | |

| hip_reconfig_readdata_o[7:0] | O | Avalon® -MM read data outputs | hip_reconfig_clk | EP/RP |

| hip_reconfig_readdatavalid_o | O | Avalon® -MM read data valid. When asserted, the data on hip_reconfig_readdata_o[7:0] is valid. | hip_reconfig_clk | EP/RP |

| hip_reconfig_write_i | I | Avalon® -MM write enable | hip_reconfig_clk | EP/RP |

| hip_reconfig_read_i | I | Avalon® -MM read enable | hip_reconfig_clk | EP/RP |

| hip_reconfig_address_i[20:0] | I | Avalon® -MM address | hip_reconfig_clk | EP/RP |

| hip_reconfig_writedata_i[7:0] | I | Avalon® -MM write data inputs | hip_reconfig_clk | EP/RP |

| hip_reconfig_waitrequest_o | O | When asserted, this signal indicates that the IP core is not ready to respond to a request. | hip_reconfig_clk | EP/RP |

| dummy_user_avmm_rst | I | Reset signal. You can tie it to ground or leave it floating when using the Hard IP Reconfiguration Interface. | EP/RP |

Reading and Writing to the Hard IP Reconfiguration Interface

Reading from the Hard IP reconfiguration interface of the P-Tile Avalon® -MM IP for PCI Express retrieves the current value at a specific address. Writing to the reconfiguration interface changes the data value at a specific address. Intel recommends that you perform read-modify-writes when writing to a register, because two or more features may share the same reconfiguration address.

Modifying the PCIe configuration registers directly affects the behavior of the PCIe device.