AN 796: Cyclone® V and Arria® V SoC Device Design Guidelines

ID

683360

Date

3/30/2022

Public

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

2. Background: Comparison between Cyclone® V SoC FPGA and Arria® V SoC FPGA HPS Subsystems

3. Design Guidelines for HPS portion of SoC FPGAs

4. Board Design Guidelines for SoC FPGAs

5. Embedded Software Design Guidelines for SoC FPGAs

A. Support and Documentation

B. Additional Information

4.2.1.1. Boot Source

4.2.1.2. Select Desired Flash Device

4.2.1.3. BSEL Options

4.2.1.4. Boot Clock

4.2.1.5. CSEL Options

4.2.1.6. Selecting NAND Flash Devices

4.2.1.7. Determine Flash Programming Method

4.2.1.8. For QSPI and SD/MMC/eMMC Provide Flash Memory Reset

4.2.1.9. Selecting QSPI Flash Devices

4.5.1. HPS EMAC PHY Interfaces

4.5.2. USB Interface Design Guidelines

4.5.3. QSPI Flash Interface Design Guidelines

4.5.4. SD/MMC and eMMC Card Interface Design Guidelines

4.5.5. NAND Flash Interface Design Guidelines

4.5.6. UART Interface Design Guidelines

4.5.7. I2C Interface Design Guidelines

4.5.8. SPI Interface Design Guidelines

5.1.1. Assembling the Components of Your Software Development Platform

5.1.2. Selecting an Operating System for Your Application

5.1.3. Assembling your Software Development Platform for Linux

5.1.4. Assembling a Software Development Platform for a Bare-Metal Application

5.1.5. Assembling your Software Development Platform for a Partner OS or RTOS

5.1.6. Choosing Boot Loader Software

5.1.7. Selecting Software Tools for Development, Debug and Trace

5.5.1.1. Enable Runtime Calibration Report

5.5.1.2. Change DLEVEL To Get More Debug Information

5.5.1.3. Enable Example Driver for HPS SDRAM

5.5.1.4. Change Data Pattern in Example Driver

5.5.1.5. Example Code to Write and Read from All Addresses

5.5.1.6. Read/Write to HPS Register in Preloader

5.5.1.7. Check HPS PLL Lock Status in Preloader

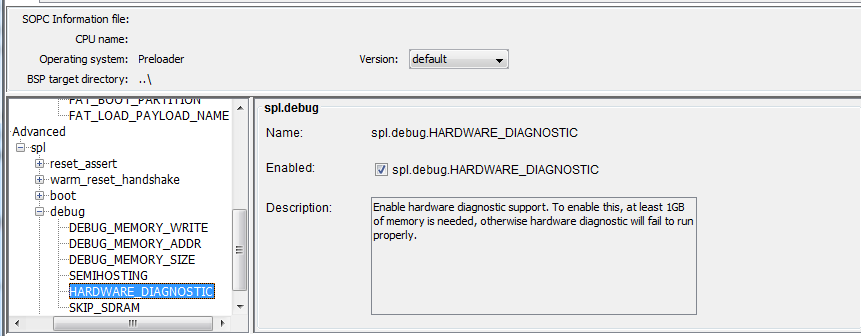

5.5.1.3. Enable Example Driver for HPS SDRAM

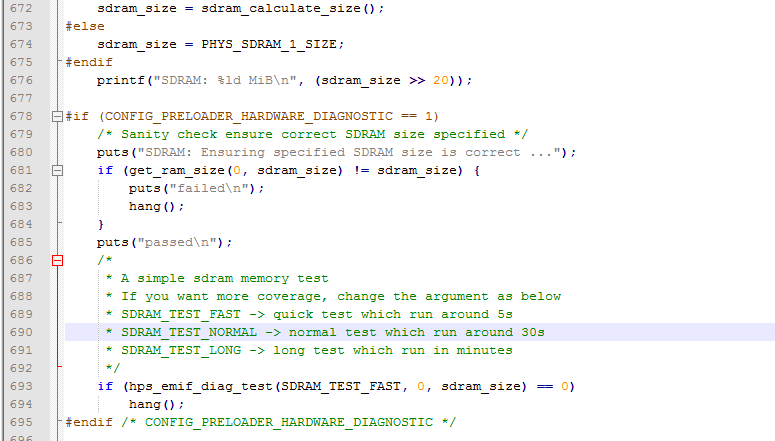

- Enable with Hardware Diagnostic Option in bsp-editor. Note: Example driver is only available in Intel® Quartus® Prime version 14.0 and later.

- PRBS31 Data pattern

- Write to random address => Read from random address

- Can select different coverage by changing parameter in spl.c