Intel® Quartus® Prime Standard Edition User Guide: Platform Designer

3.1.5.2.2. Fixed Priority Arbitration with AXI Masters and Avalon® -MM Slaves

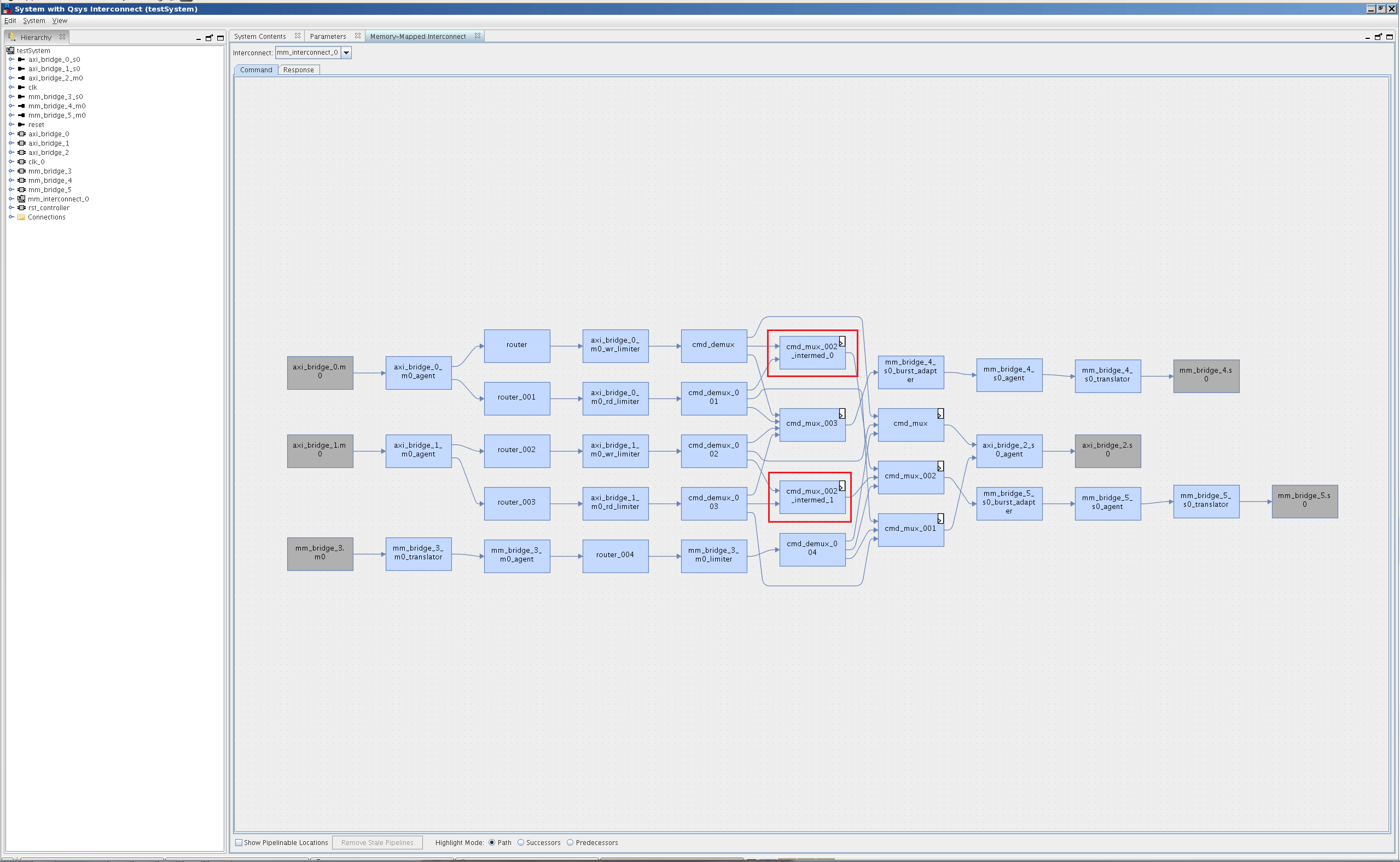

Since AXI masters have separate read and write channels, each channel appears as two separate masters to the Avalon® -MM slave. To support fairness between the AXI master’s read and write channels, the instantiated round-robin intermediary multiplexer arbitrates between simultaneous read and write commands from the AXI master to the fixed-priority Avalon® -MM slave.

When an AXI master is connected to a fixed priority AXI slave, the master’s read and write channels are directly connected to the AXI slave’s fixed-priority multiplexers. In this case, there is one multiplexer for the read command, and one multiplexer for the write command and therefore an intermediary multiplexer is not required.

The red circles indicate placement of the intermediary multiplexer between the AXI master and Avalon® -MM slave due to the separate read and write channels of the AXI master.