4.7.4. 6.144-Gbps Support Capability in Cyclone V GT Devices

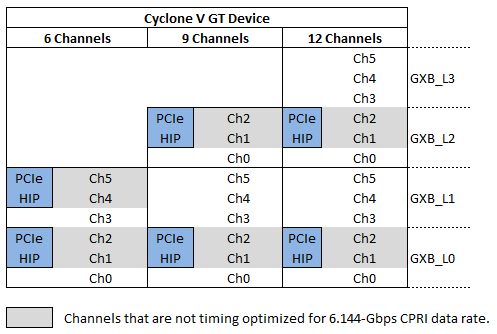

The maximum number of CPRI channels allowed for 9-channel and 12-channel devices is as follows. The same limitation applies to devices with fewer transceiver channels.

- For a 9-channel device, you can implement a maximum of 4 full duplex 6.144-Gbps CPRI-compliant channels.

- For a 12-channel device, you can implement a maximum of 6 full duplex 6.144-Gbps CPRI-compliant channels.

You must increase the voltage on VCCE_GXB and VCCL_GXB to 1.2 V to support the maximum number of channels.

The reference clock frequency for the 6.144 Gbps CPRI channel must be ≥ 307.2 MHz.

The maximum number of transceiver channels in a Cyclone V GT device that can achieve 6.144-Gbps CPRI compliance is based on:

- Transceiver performance in meeting the TX jitter specification for 6.144-Gbps CPRI.

- CPRI channels with an auto-rate negotiation capability from 1228.8 Mbps to 6.144 Gbps.

- 6.144-Gbps CPRI channel restriction based on the following figure.

The channels next to a PCIe Hard IP block are not timing optimized for the 6.144-Gbps CPRI data rate. Affected channels are shaded in gray in the above figure. Avoid placing the 6.144-Gbps CPRI channels in the affected channels. The affected channels can still be used as a CMU for the CPRI channels.