Video and Vision Processing Suite Intel® FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

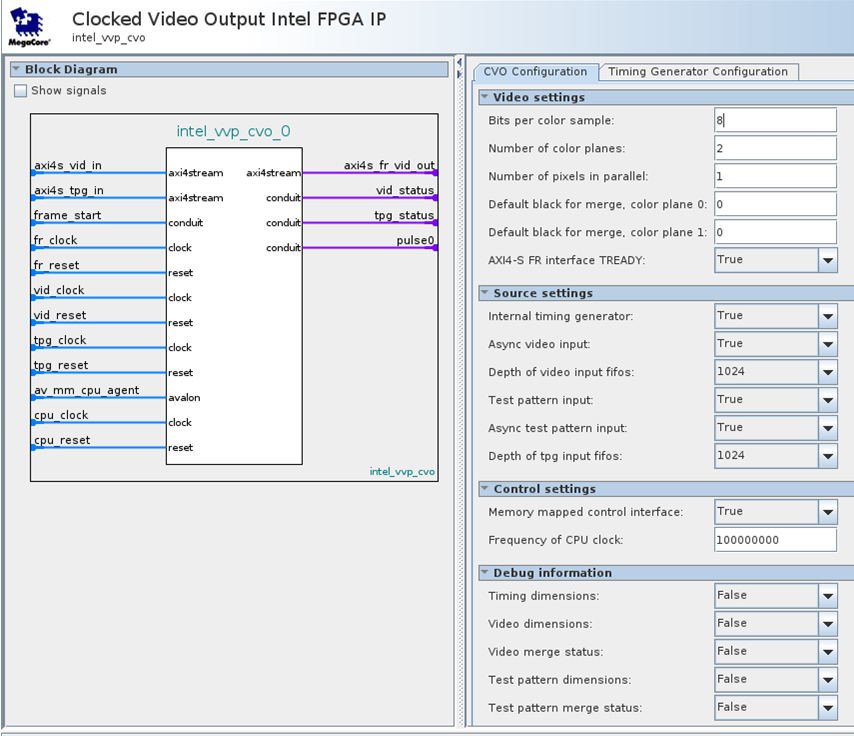

14.2. Clocked Video Output IP Parameters

| Parameter | Allowed Range | Description |

|---|---|---|

| Video Settings | ||

| Number of pixels in parallel | 1 to 8 | Select the number of pixels in parallel |

| Number of color planes | 1 to 4 | Select the number of color planes per pixel |

| Bits per color sample | 8 to 16 | Select the number of bits per color sample |

| Default black for merge, color plane 0 | 0 to 65535 | The initial value of black for this color plane |

| Default black for merge, color plane 1 | 0 to 65535 | The initial value of black for this color plane |

| Default black for merge, color plane 2 | 0 to 65535 | The initial value of black for this color plane |

| Default black for merge, color plane 3 | 0 to 65535 | The initial value of black for this color plane |

| AXI4-S FR interface TREADY | True or False | Select True to include the tReady signal in the full-raster interface Select False to remove the tReady signal |

| Source Settings | ||

| Internal Timing Generator | True or False | If True, the IP includes the Video Timing Generator Intel IP If False, the IP provides an AXI4-S full-raster input bus for an external video timing source. |

| Async Video Input | True or False | If True, the IP sees the video input as asynchronous to the AXI4-S full-raster output. If False, the video input and AXI4-S full-raster output must use the same clock. |

| Depth of Video Input Fifos | 0, 512, 1024, 2048, 4096 | The approximate size of the FIFO buffer to use for the video input path. If set to 0, the IP registers the path internally to improve timing performance. |

| Test Pattern Input | True or False | If True, an additional AXI4-S lite or full input bus is generated. If the primary input bus fails for any reason, this additional input is used. If False, the IP generates no additional AXI4-S lite or full input buses. If the primary input bus fails for any reason, the output goes to black. |

| Async Test Pattern Input | True or False | If True, the TPG input is asynchronous to the AXI4-S FR output. If False, the test pattern generator input and AXI4-S full-raster output must use the same clock. |

| Depth of TPG Input Fifos | 0, 512, 1024, 2048, 4096 | The approximate size of the FIFO buffer to use for the test pattern generator input path. If set to 0, the IP registers the path internally to improve timing performance. |

| Control Settings | ||

| Memory-Mapped Control Interface | True or False | Select True to turn on the processor interface and associated signals. When False, the IP removes the processor interface. All processor registers use default values |

| Frequency of CPU Clock 25 | 1 to 1000000000 | The frequency, in Hz, of the processor clock. |

| Debug Settings | ||

| Timing Dimensions | True or False | Select True to turn on the timing dimension processor registers. Additional logic is generated to measure the active and total widths and heights of the timing input, the FR clock frequency, and the FR frame period. Select False, and the IP generates no additional logic. The associated processor registers return 0x1234abcd. |

| Video Dimensions | True or False | Select True to turn on the video dimension processor registers. The IP generates additional logic to measure the active width and height of the video input, the video clock frequency, and the video input frame period. Select False, and the IP generates no additional logic. The associated processor registers return 0x1234abcd. |

| Video Merge Status | True or False | Select True to turn on diagnostic counters that report the status of the video merge process. Select False, and the IP generates no additional logic. The associated processor registers return 0x1234abcd. |

| Test Pattern Dimensions | True or False | Select True to turn on the test pattern generator dimension processor registers. The IP generates additional logic to measure the active width and height of the test pattern generator input, the test pattern generator clock frequency, and the test pattern generator input frame period Select False, and the IP generates no additional logic. The associated processor registers return 0x1234abcd. |

| Test Pattern Merge Status | True or False | Select True to turn on diagnostic counters that report the status of the test pattern generator merge process. Select False, and the IP generates no additional logic. The associated processor registers return 0x1234abcd. |

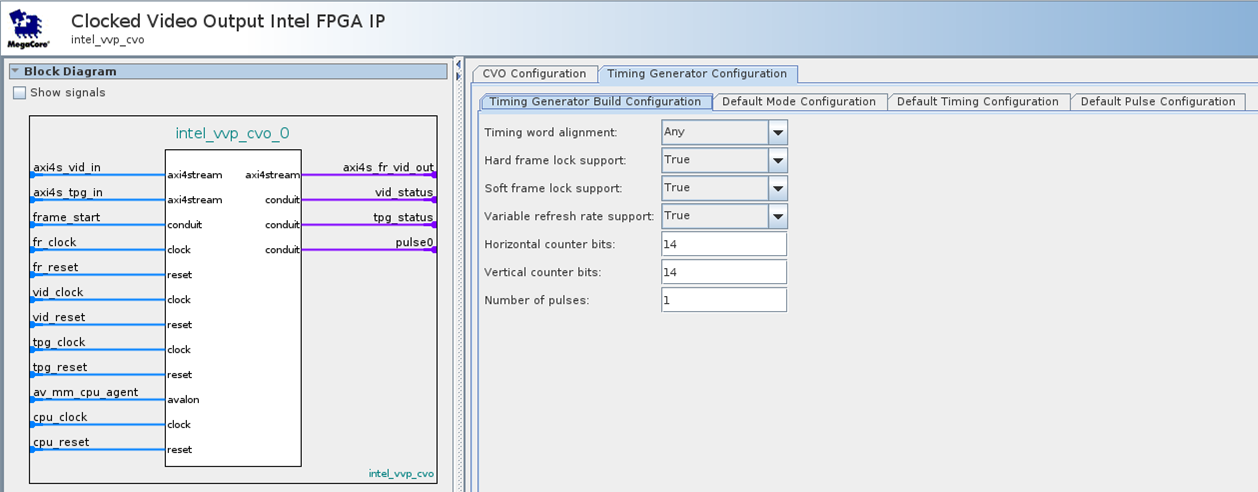

| Parameters | Allowed Range | Description |

|---|---|---|

| Timing Word Alignment | Any or PIP-Aligned Only |

Select Any for no restrictions on raster dimensions versus the number of pixels in parallel. When PIP-Aligned Only, all timing parameters must be integer multiples of the pixels In parallel value. |

| Hard frame lock support | True or False | Select True to turn on the hard frame lock support. When False, the IP removes all frame lock support. |

| Soft frame lock support | True or False | Select True to enable soft frame lock support. 26When False, the IP removes soft frame lock support. |

| Variable refresh rate support | True or False | Select True to turn on variable refresh rate support When False, the IP removes support for variable refresh rate |

| Horizontal counter bits | 4-16 | The number of binary bits required to represent the maximum width of raster. For example, for a 4096 wide raster, set to 13. |

| Vertical counter bits | 4-16 | The number of binary bits required to represent the maximum height of raster. For example, for a 2048 high raster, set to 12. |

| Number of pulses | 0-8 | The number of additional general-purpose pulses that the IP can produce. Each additional pulse increases the gate count of this IP. If set to 0, the Default Pulse Configuration GUI turns off. |

Hard Frame Lock must also be True for correct operation of soft frame lock