High Bandwidth Memory (HBM2) Interface Intel® FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

6.3.3. Improving User Logic to HBM2 Controller AXI Interface Timing

Controller Backpressure Latency

The Controller Backpressure Latency feature allows the user interface to interface to the controller READY signals (address write, address read and write channels) with flexibility. When you enable this feature, the READY signals provided by the HBM2 controller are issued early, according to a value that you specify.

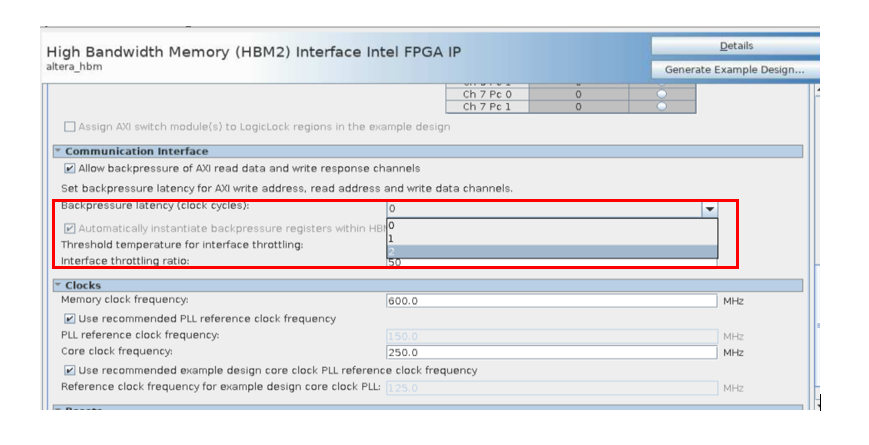

By default, this feature is disabled, with a backpressure latency of 0 clock cycles. When you enable this feature, you specify a desired backpressure latency of 1 or 2 clock cycles. The READY signals provided by the HBM2 controller — AXI Write Address Ready (AXI_X_Y_AWREADY), AXI Read Address Ready (AXI_X_Y_ARREADY) and AXI Write Data Ready (AXI_X_Y_WREADY) — are then issued early by the number of cycles that you specified.

When this feature is enabled, set to N cycles (supported clock cycle values for N are 1, 2 when the feature is enabled and 0 when disabled), the READY signals provided by the HBM2 Controller (that is, AXI Write Address Ready (AXI_X_Y_AWREADY), AXI Read Address Ready (AXI_X_Y_ARREADY) and AXI Write Data Ready (AXI_X_Y_WREADY)) are issued N clock cycles early. Controller Backpressure Latency is enabled across all the AXI interfaces for the selected HBM2 interface.

When you choose a non-zero backpressure register value, you can choose to add the register stages in either of the following ways:

- You can allow the HBM2 IP to add the registers in the soft logic adaptor on the AXI interface; this is the default behavior.

- You can handle the AXI interface timing (early READY deassertion) manually, by disabling the Automatically instantiate back pressure registers within HBM2 IP option.

Using AXI Backpressure Latency

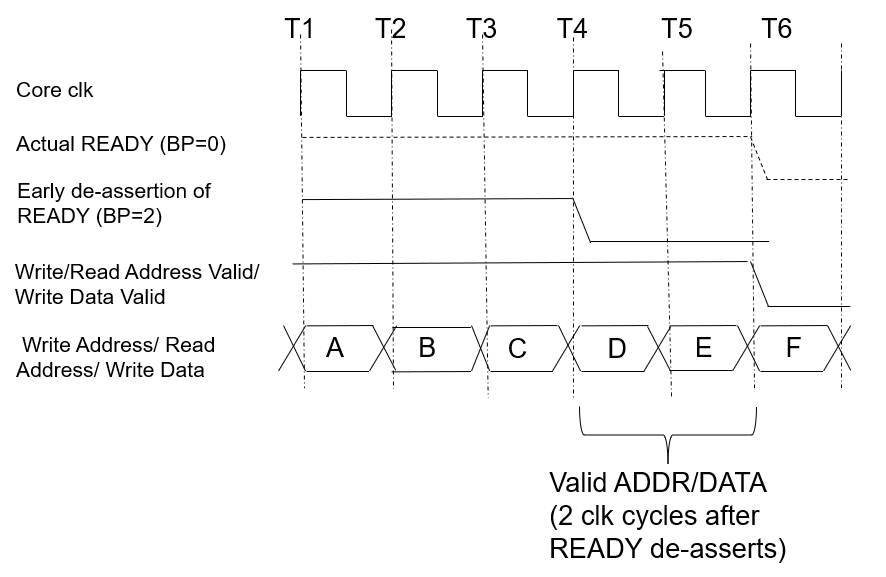

The following timing diagram illustrates backpressure latency of two clock cycles. This value enables the deassertion of the READY signals to happen two core clock cycles earlier than otherwise. Backpressure latency of 2 clock cycles provides the user interface two additional clock cycles to respond to the READY deassertion by continuing to provide valid Write Address/Write Data and Read Address for two clock cycles after the READY deassertion.

As illustrated in the diagram below, with backpressure latency of two clock cycles, READY deasserts in clock cycle T4; however, the HBM2 controller continues to accept input in clock cycles T4 and T5 (input D and E) provided that the corresponding VALID signal is active.

Using the Early READY Signal to Facilitate Timing Closure

When you specify a non-zero AXI backpressure latency of N, you can also add a total of N pipeline registers in the AXI interface outputs and the READY inputs from the HBM2 controller. By ensuring the total pipeline registers added in both Input and Output directions is N, you can ease timing closure. You can enable the HBM2 IP to generate these registers from the HBM2 IP parameter editor.

Beginning in the Intel® Quartus® Prime software version 19.4, the HBM2 IP adds the following registers based on the Backpressure latency setting; it is no longer necessary to manually insert the registers.

- When Backpressure latency is set to 1, the controller deasserts the READY signal one clock cycle early. A single register stage is added in signals in the AXI Interface Valid path from the core to the HBM2 controller.

- When Backpressure latency is set to 2, the controller deasserts the READY signal two clock cycles early. The HBM2 IP adds the following registers:

- One register stage is added on the AXI Interface Valid and all related AXI interface signals from the user logic.

- One register stage is added on READY signals (AWREADY, WREADY, ARREADY) from the controller to the core.

The following figure illustrates the backpressure register placement in the data path between the user core logic and the AXI soft logic adaptor to facilitate timing closure.

Write Response and Read Data Interface Timing

When you enable the read and write response backpressure feature, Write response and Read data interface timing must still be treated at zero cycle latency. The user-interface-issued BREADY and RREADY must be driven HIGH to ensure the controller can provide the outputs when applicable.

When you disable the read and write response backpressure feature, you can add pipeline registers to read and write response outputs, because BREADY and RREADY are always HIGH, indicating that the user interface is ready to accept response at any time.