DSP Builder for Intel® FPGAs (Advanced Blockset): Handbook

A newer version of this document is available. Customers should click here to go to the newest version.

13.1.3. Channel Viewer (ChanView)

You can use a ChanView block in a testbench to visualize the contents of the TDM protocol. It produces synthesizable RTL, so you can use it anywhere in your design.

When a single channel is input, the ChanView block strips out all the non-valid samples, thus cleaning up the display in the Simulink scope.

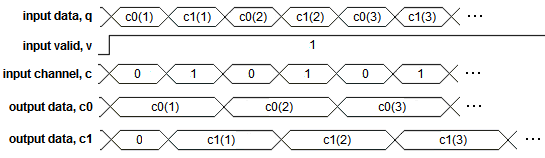

The channel outputs are not aligned. For example, if you have input channels c0 and c1 on a single wire and view both channels, the output is not aligned.

| Parameter | Description |

|---|---|

| Number of input channels | Specifies the number of unique channels the block can process. The design does not use this parameter unless the data bus is a vector or the folding factor is greater than the number of channels. If the data bus is a vector, this value determines which vector element contains the correct channel. |

| Output channels | A vector that controls the input channels to decode and present as outputs. The number of outputs equals the length of this vector, and each output corresponds to one channel in order. |

| Signal | Direction | Description |

|---|---|---|

| q | Input | The data input to the block. This signal may be a vector. This block does not support floating-point types. |

| v | Input | Indicates validity of data input signals. If v is high, the data on the wire is valid. |

| c | Input | Indicates the channel of the data input signals. If v is high, c indicates which channel the data corresponds to. |

| cn | Output | Each output is a deserialized version of the channel contained on the TDM bus. The output value is updated on each clock cycle that has valid data when the channel matches the required channel. |

| ov | Output | Optional. Pulses 1 at last cycle of a frame (when all held channel output signals have correct value for the frame) provided valid is high throughout the frame data. |

After DSP Builder runs a simulation, it updates the help pages with specific information about each instance of a block. For resource usage, on the DSP Builder menu, point to Resources, and click Design.

| Message Example | Description |

|---|---|

| Written on Tue Feb 19 11:25:27 2008 | Date and time when you ran this file. |

| Latency is 2 | The latency that this block introduces. |

| Port interface table | Lists the port interfaces to the ChanView block. |