DSP Builder for Intel® FPGAs (Advanced Blockset): Handbook

A newer version of this document is available. Customers should click here to go to the newest version.

12.1.5. Decimating CIC

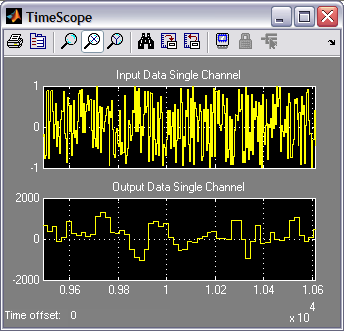

You can use the DecimatingCIC block in a digital down converter for a radio system or a general purpose DSP application. The coefficients and input data are fixed-point types, and the output is the implied full-precision fixed-point type. You can reduce the precision with a separate Scale block, which can perform rounding and saturation to provide the required output precision.

The DecimatingCIC block supports rate changes from two upwards.

The DecimatingCIC has a lower output sample rate than the input sample rate by a factor D, where D is the decimation factor. Usually, the DecimatingCIC discards (D–1) out of D output samples thus lowering the sample rate by a factor D. The physical implementation avoids performing additions leading to these discarded samples, reducing the filter cost.

| Parameter | Description |

|---|---|

| Input rate per channel | Specifies the sampling frequency of the input data per channel measured in millions of samples per second (MSPS). |

| Number of channels | Specifies the number of unique channels to process. |

| Number of stages | Specifies the number of comb and integrator stages. |

| Decimation factor | Specifies the decimation factor 1/(integer). (An integer greater than 1 implies interpolation.) |

| Differential delay | Specifies the differential delay. |

| Signal | Direction | Description |

|---|---|---|

| a | Input | The fixed-point data input to the block. If you request more channels than can fit on a single bus, this signal is a vector. The width in bits is inherited from the input wire. |

| v | Input | Indicates validity of the data input signals. If v is high, the data on the a wire is valid. |

| c | Input | Indicates channel of data input signals. If v is high, c indicates which channel the data corresponds to. |

| bypass | Input | When this input asserts, the input data is zero-stuffed and scaled by the gain of the filter, which is useful during hardware debugging. |

| q | Output | The data output from the block. If you request more channels than can fit on a single bus, this signal is a vector. The width in bits is a function of the input width in bits and the parameterization. |

| v | Output | Indicates validity of data output signals. |

| c | Output | Indicates channel of data output signals. |