Arria® 10 and Cyclone® 10 GX Avalon® Memory-Mapped (Avalon-MM) Interface for PCI Express* User Guide

ID

683724

Date

9/10/2024

Public

1. Datasheet

2. Quick Start Guide

3. Parameter Settings

4. Physical Layout

5. 64- or 128-Bit Avalon-MM Interface to the Endpoint Application Layer

6. Registers

7. Reset and Clocks

8. Interrupts for Endpoints

9. Error Handling

10. Design Implementation

11. Throughput Optimization

12. Additional Features

13. Avalon-MM Testbench and Design Example

14. Avalon-MM Testbench and Design Example for Root Port

15. Hard IP Reconfiguration

16. Debugging

A. PCI Express Protocol Stack

B. Transaction Layer Packet (TLP) Header Formats

C. Lane Initialization and Reversal

D. Arria® 10 or Cyclone® 10 GX Avalon® -MM Interface for PCIe* Solutions User Guide Archive

E. Document Revision History

1.1. Arria® 10 or Cyclone® 10 GX Avalon-MM Interface for PCIe Datasheet

1.2. Features

1.3. Release Information

1.4. Device Family Support

1.5. Configurations

1.6. Design Examples

1.7. IP Core Verification

1.8. Resource Utilization

1.9. Recommended Speed Grades

1.10. Creating a Design for PCI Express

3.1. Parameters

3.2. Avalon-MM Settings

3.3. Base Address Register (BAR) Settings

3.4. Device Identification Registers

3.5. PCI Express and PCI Capabilities Parameters

3.6. Configuration, Debug, and Extension Options

3.7. Vendor Specific Extended Capability (VSEC)

3.8. PHY Characteristics

3.9. Example Designs

5.1. 32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave Signals

5.2. Bursting and Non-Bursting Avalon® -MM Module Signals

5.3. 64- or 128-Bit Bursting TX Avalon-MM Slave Signals

5.4. Clock Signals

5.5. Reset, Status, and Link Training Signals

5.6. Interrupts for Endpoints when Multiple MSI/MSI-X Support Is Enabled

5.7. Hard IP Status Signals

5.8. Physical Layer Interface Signals

6.1. Correspondence between Configuration Space Registers and the PCIe Specification

6.2. Type 0 Configuration Space Registers

6.3. Type 1 Configuration Space Registers

6.4. PCI Express Capability Structures

6.5. Intel-Defined VSEC Registers

6.6. CvP Registers

6.7. 64- or 128-Bit Avalon-MM Bridge Register Descriptions

6.8. Programming Model for Avalon-MM Root Port

6.9. Uncorrectable Internal Error Mask Register

6.10. Uncorrectable Internal Error Status Register

6.11. Correctable Internal Error Mask Register

6.12. Correctable Internal Error Status Register

6.7.1.1. Avalon-MM to PCI Express Interrupt Status Registers

6.7.1.2. Avalon-MM to PCI Express Interrupt Enable Registers

6.7.1.3. PCI Express Mailbox Registers

6.7.1.4. Avalon-MM-to-PCI Express Address Translation Table

6.7.1.5. PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

6.7.1.6. Avalon-MM Mailbox Registers

6.7.1.7. Control Register Access (CRA) Avalon-MM Slave Port

13.5.1. ebfm_barwr Procedure

13.5.2. ebfm_barwr_imm Procedure

13.5.3. ebfm_barrd_wait Procedure

13.5.4. ebfm_barrd_nowt Procedure

13.5.5. ebfm_cfgwr_imm_wait Procedure

13.5.6. ebfm_cfgwr_imm_nowt Procedure

13.5.7. ebfm_cfgrd_wait Procedure

13.5.8. ebfm_cfgrd_nowt Procedure

13.5.9. BFM Configuration Procedures

13.5.10. BFM Shared Memory Access Procedures

13.5.11. BFM Log and Message Procedures

13.5.12. Verilog HDL Formatting Functions

A.4.1. Avalon‑MM Bridge TLPs

A.4.2. Avalon-MM-to-PCI Express Write Requests

A.4.3. Avalon-MM-to-PCI Express Upstream Read Requests

A.4.4. PCI Express-to-Avalon-MM Read Completions

A.4.5. PCI Express-to-Avalon-MM Downstream Write Requests

A.4.6. PCI Express-to-Avalon-MM Downstream Read Requests

A.4.7. Avalon-MM-to-PCI Express Read Completions

A.4.8. PCI Express-to-Avalon-MM Address Translation for 32-Bit Bridge

A.4.9. Minimizing BAR Sizes and the PCIe Address Space

A.4.10. Avalon® -MM-to-PCI Express Address Translation Algorithm for 32-Bit Addressing

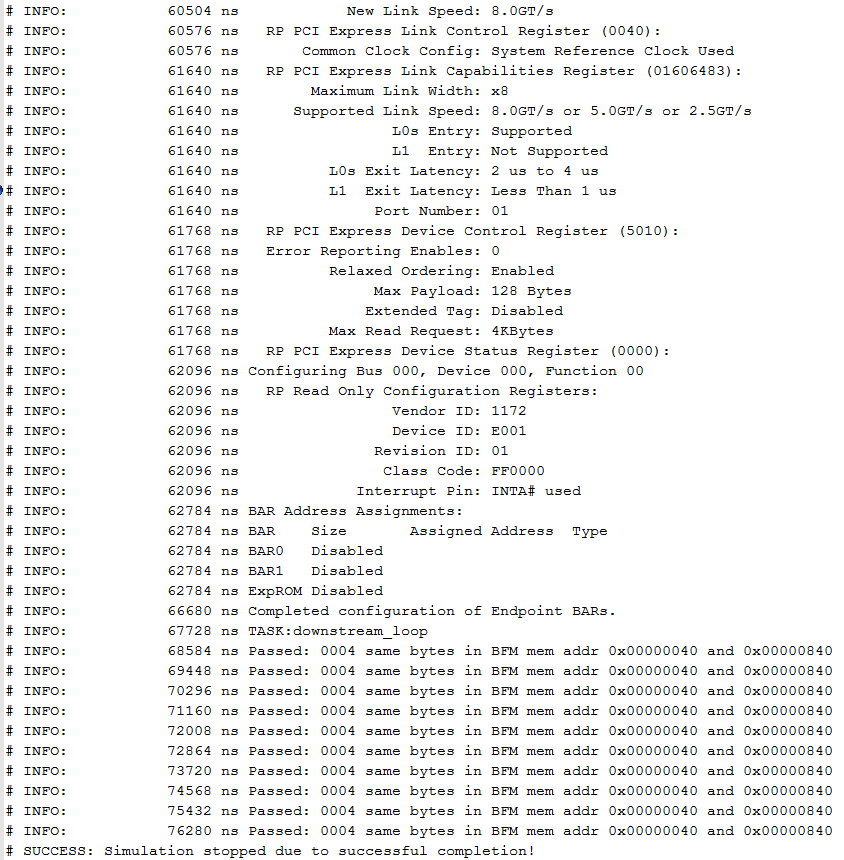

2.4. Simulating the Design

Figure 7. Procedure

- Change to the testbench simulation directory.

- Run the simulation script for the simulator of your choice. Refer to the table below.

- Analyze the results.

| Simulator | Working Directory | Instructions |

|---|---|---|

| ModelSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/mentor/ |

|

| VCS* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/synopsys/vcs |

|

| NCSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/cadence |

|

| Xcelium* Parallel Simulator | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/xcelium |

|

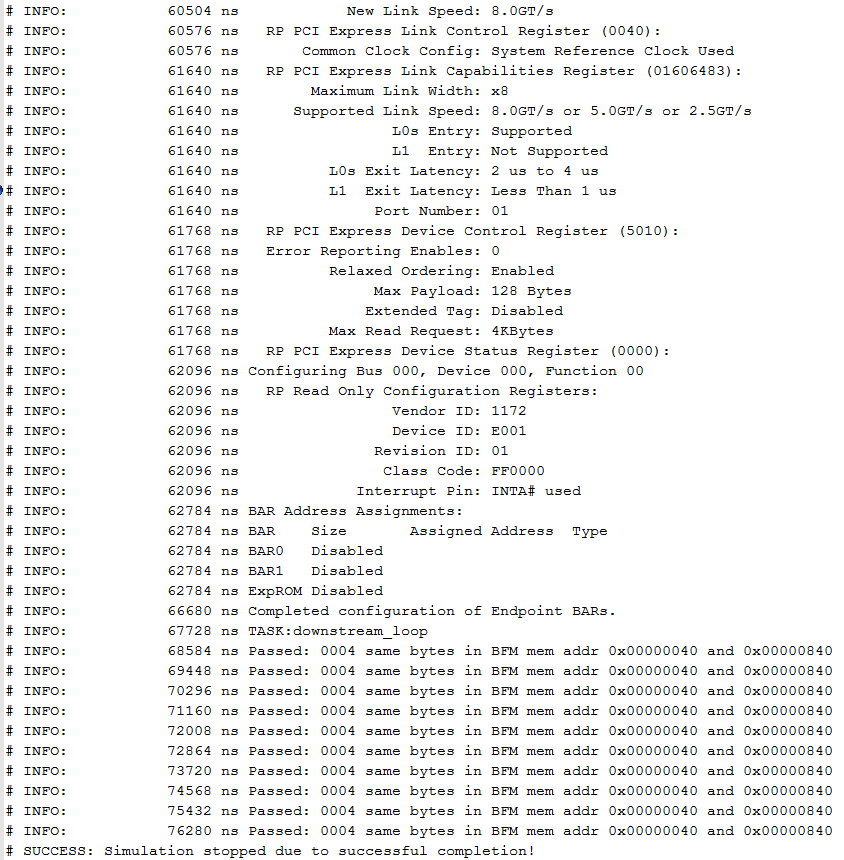

Figure 8. Partial Transcript from Successful Endpoint Avalon-ST PIO Simulation Testbench