Intel® Quartus® Prime Standard Edition User Guide: Design Recommendations

ID

683323

Date

9/24/2018

Public

2.1. Using Provided HDL Templates

2.2. Instantiating IP Cores in HDL

2.3. Inferring Multipliers and DSP Functions

2.4. Inferring Memory Functions from HDL Code

2.5. Register and Latch Coding Guidelines

2.6. General Coding Guidelines

2.7. Designing with Low-Level Primitives

2.8. Recommended HDL Coding Styles Revision History

2.4.1.1. Use Synchronous Memory Blocks

2.4.1.2. Avoid Unsupported Reset and Control Conditions

2.4.1.3. Check Read-During-Write Behavior

2.4.1.4. Controlling RAM Inference and Implementation

2.4.1.5. Single-Clock Synchronous RAM with Old Data Read-During-Write Behavior

2.4.1.6. Single-Clock Synchronous RAM with New Data Read-During-Write Behavior

2.4.1.7. Simple Dual-Port, Dual-Clock Synchronous RAM

2.4.1.8. True Dual-Port Synchronous RAM

2.4.1.9. Mixed-Width Dual-Port RAM

2.4.1.10. RAM with Byte-Enable Signals

2.4.1.11. Specifying Initial Memory Contents at Power-Up

2.6.6.1. If Performance is Important, Optimize for Speed

2.6.6.2. Use Separate CRC Blocks Instead of Cascaded Stages

2.6.6.3. Use Separate CRC Blocks Instead of Allowing Blocks to Merge

2.6.6.4. Take Advantage of Latency if Available

2.6.6.5. Save Power by Disabling CRC Blocks When Not in Use

2.6.6.6. Initialize the Device with the Synchronous Load (sload) Signal

3.4.1. Apply Complete System-Centric Timing Constraints for the Timing Analyzer

3.4.2. Force the Identification of Synchronization Registers

3.4.3. Set the Synchronizer Data Toggle Rate

3.4.4. Optimize Metastability During Fitting

3.4.5. Increase the Length of Synchronizers to Protect and Optimize

3.4.6. Set Fitter Effort to Standard Fit instead of Auto Fit

3.4.7. Increase the Number of Stages Used in Synchronizers

3.4.8. Select a Faster Speed Grade Device

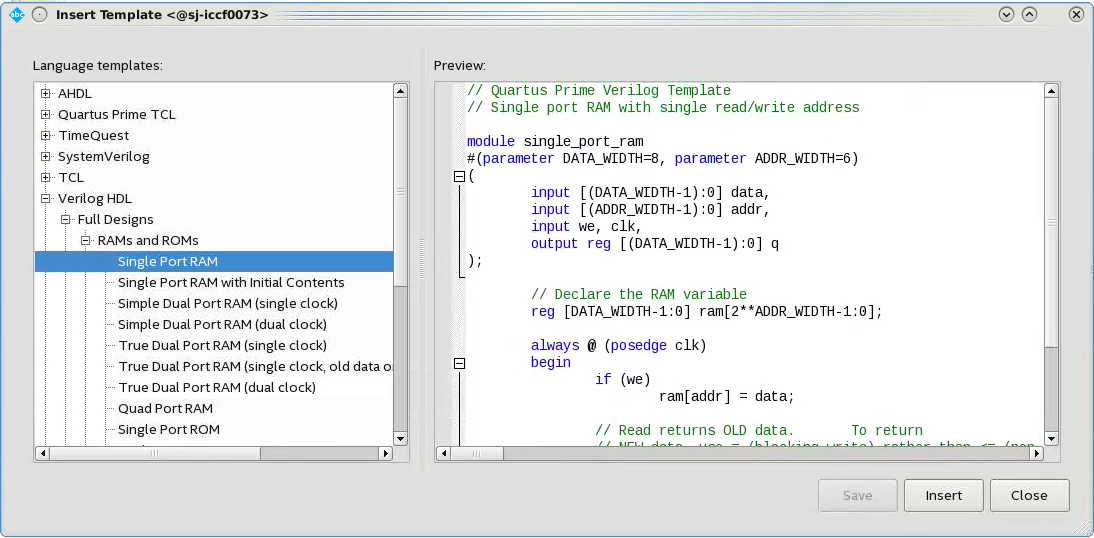

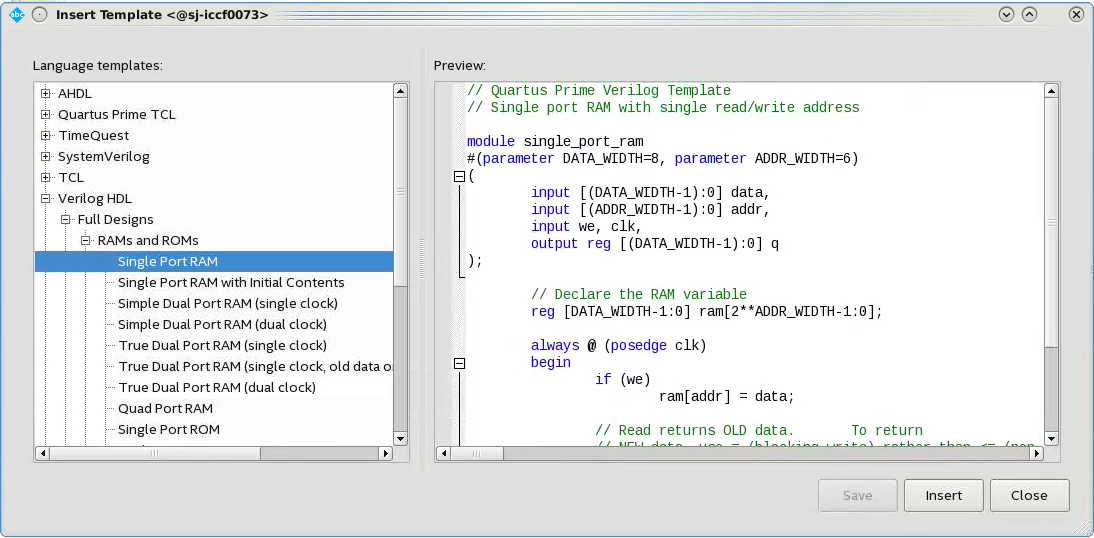

2.1.1. Inserting HDL Code from a Provided Template

- Click File > New.

- In the New dialog box, select the HDL language for the design files: SystemVerilog HDL File, VHDL File, or Verilog HDL File; and click OK.

A text editor tab with a blank file opens.

- Right-click the blank file and click Insert Template.

- In the Insert Template dialog box, expand the section corresponding to the appropriate HDL, then expand the Full Designs section.

- Select a template.

The template now appears in the Preview pane.

- To paste the HDL design into the blank Verilog or VHDL file you created, click Insert.

- Click Close to close the Insert Template dialog box.

Figure 21. Inserting a RAM Template

Note: Use the Intel® Quartus® Prime Text Editor to modify the HDL design or save the template as an HDL file to edit in your preferred text editor.