External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

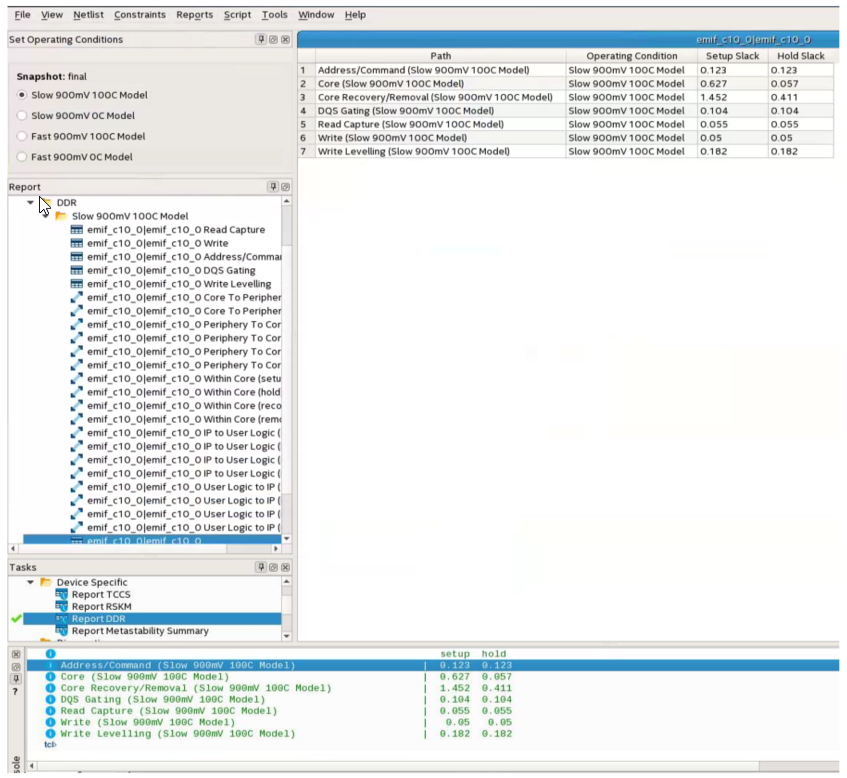

8.2. Timing Report DDR

This <variation_name>_report_timing.tcl script reports the following timing slacks on specific paths of the DDR SDRAM:

- Read capture

- Read resynchronization

- Mimic, address and command

- Core

- Core reset and removal

- Half-rate address and command

- DQS versus CK

- Write

- Write leveling (tDQSS)

- Write leveling (tDSS/tDSH)

- DQS Gating (Postamble)

The <variation_name>_report_timing.tcl script checks basic design rules and assumptions; if violations are found, you receive critical warnings when the Timing Analyzer runs during compilation or when you run the Report DDR task.

To generate a timing margin report, follow these steps:

- Compile your design in the Intel® Quartus® Prime software.

- Launch the Timing Analyzer.

- Double-click Report DDR from the Tasks pane. This action automatically executes the Create Timing Netlist, Read SDC File, and Update Timing Netlist tasks for your project.

- The .sdc may not be applied correctly if the variation top-level file is the top-level file of the project. You must have the top-level file of the project instantiate the variation top-level file.

The Report DDR feature creates a new DDR folder in the Timing Analyzer Report pane.

Expanding the DDR folder reveals the detailed timing information for each PHY timing path, in addition to an overall timing margin summary for the instance, as shown in the following figure.