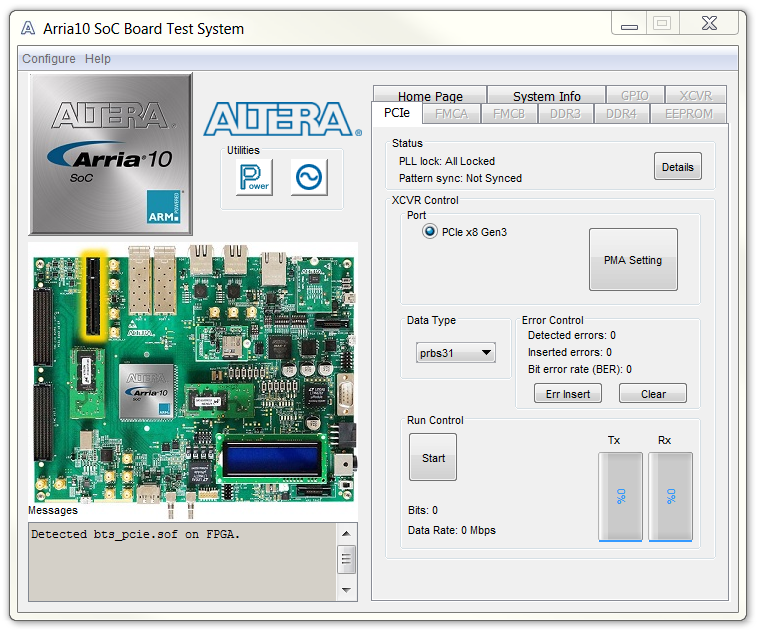

4.4.5. The PCIe* Tab

This tab allows you to run a PCIe* loopback test on your board. You can also load the design and use an oscilloscope to measure an eye diagram of the PCIe* transmit signals.

Figure 16. The PCIe* Tab

Status

Displays the following status information during a loopback test:

- PLL lock: Shows the PLL locked or unlocked state.

- Pattern sync: Shows the pattern synced or not synced state. The pattern is considered synced when the start of the data sequence is detected.

- Details: Shows the PLL lock and pattern sync status.

Figure 17. PCIe* Tab: PLL and Pattern Status

Port

PCIe* x8 Gen3

PMA Setting

Allows you to make changes to the PMA parameters that affect the active transceiver interface. The following settings are available for analysis:

- Serial Loopback: Routes signals between the transmitter and the receiver.

- VOD: Specifies the voltage output differential of the transmitter buffer.

- Pre-emphasis tap:

- 1st pre: Specifies the amount of pre-emphasis on the pre-tap of the transmitter buffer.

- 2nd pre: Specifies the amount of pre-emphasis on the second pre-tap of the transmitter buffer.

- 1st post: Specifies the amount of pre-emphasis on the first post tap of the transmitter buffer.

- 2nd post: Specifies the amount of pre-emphasis on the second post tap of the transmitter buffer.

- Equalizer: Specifies the AC gain setting for the receiver equalizer in four stage mode.

- DC gain: Specifies the DC gain setting for the receiver equalizer in four stage mode.

- VGA: Specifies the VGA gain value.

Figure 18. PCIe* Tab: Set PMA Values

Data Type

Specifies the type of data contained in the transactions. The following data types are available for analysis:

- PRBS 7: Selects pseudo-random 7-bit sequences.

- PRBS 15: Selects pseudo-random 15-bit sequences.

- PRBS 23: Selects pseudo-random 23-bit sequences.

- PRBS 31: Selects pseudo-random 31-bit sequences.

- HF: Selects highest frequency divide-by-2 data pattern 10101010.

- LF: Selects lowest frequency divide-by-33 data pattern.

Error Control

Displays data errors detected during analysis and allows you to insert errors:

- Detected errors: Displays the number of data errors detected in the hardware.

- Inserted errors: Displays the number of errors inserted into the transmit data stream.

- Insert Error: Inserts a one-word error into the transmit data stream each time you click the button. Insert Error is only enabled during transaction performance analysis.

- Clear: Resets the Detected errors and Inserted errors counters to zeroes.

Run Control

- Start: Initiates the selected ports transaction performance analysis.

Note: Always click Clear before Start.

- Stop: Terminates transaction performance analysis.

- TX and RX performance bars: Show the percentage of maximum theoretical data rate that the requested transactions are able to achieve.