1. Stratix® 10 Variable Precision DSP Blocks Overview

2. Block Architecture Overview

3. Operational Mode Descriptions

4. Design Considerations

5. Stratix® 10 Variable Precision DSP Blocks Implementation Guide

6. Native Fixed Point DSP Stratix® 10 FPGA IP Core References

7. Multiply Adder IP Core References

8. ALTMULT_COMPLEX Intel® FPGA IP Core References

9. LPM_MULT Intel® FPGA IP Core References

10. Native Floating Point DSP Stratix® 10 FPGA IP References

11. LPM_DIVIDE (Divider) Intel FPGA IP Core

12. Stratix® 10 Variable Precision DSP Blocks User Guide Document Archives

13. Document Revision History for the Stratix® 10 Variable Precision DSP Blocks User Guide

2.1. Input Register Bank for Fixed-Point and Floating-Point Arithmetic

2.2. Pipeline Registers for Fixed-Point and Floating-Point Arithmetic

2.3. Pre-adder for Fixed-Point Arithmetic

2.4. Internal Coefficient for Fixed-Point Arithmetic

2.5. Multipliers for Fixed-Point and Floating-Point Arithmetic

2.6. Adder or Subtractor for Fixed-Point and Floating-Point Arithmetic

2.7. Accumulator, Chainout Adder, and Preload Constant for Fixed-Point Arithmetic

2.8. Systolic Register for Fixed-Point Arithmetic

2.9. Double Accumulation Register for Fixed-Point Arithmetic

2.10. Output Register Bank for Fixed-Point and Floating-Point Arithmetic

2.11. Exception Handling for Floating-Point Arithmetic

7.2.1.2. Pre-adder Coefficient Mode

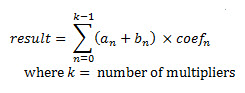

In this mode, one multiplier operand derives from the pre-adder, and the other operand derives from the internal coefficient storage. The coefficient storage allows up to 8 preset constants. The coefficient selection signals are coefsel[0..3].

This mode is expressed in the following equation.

The following shows the pre-adder coefficient mode of a multiplier.

Figure 34. Pre-adder Coefficient Mode