AN 766: Intel® Stratix® 10 Devices, High Speed Signal Interface Layout Design Guideline

ID

683132

Date

3/12/2019

Public

Intel® Stratix® 10 Devices and Transceiver Channels

PCB Stackup Selection Guideline

Recommendations for High Speed Signal PCB Routing

FPGA Fan-out Region Design

CFP2/CFP4 Connector Board Layout Design Guideline

QSFP+/zSFP/QSFP28 Connector Board Layout Design Guideline

SMA 2.4-mm Layout Design Guideline

Tyco/Amphenol Interlaken Connector Design Guideline

Electrical Specifications

Document Revision History for AN 766: Intel® Stratix® 10 Devices, High Speed Signal Interface Layout Design Guideline

Option 1: Via-In-Pad Topology

Option 2: Dog-bone with GND Cutout at BGA Pad Topology

Option 3: Micro-via Topology

GND Cutout Under BGA Pads in Fan-out Configuration

Comparison of Dog-bone with GND Cutout Under the BGA and Via-in-Pad Configurations

Trace Shape Routing at the BGA Void Area (Tear Drop Configuration)

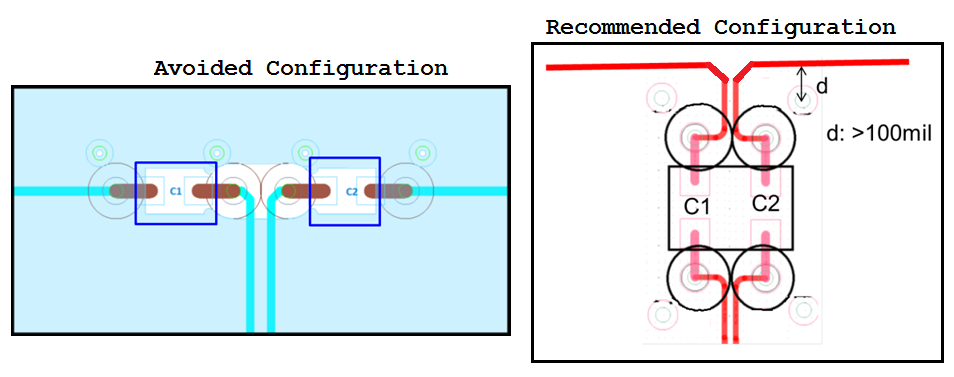

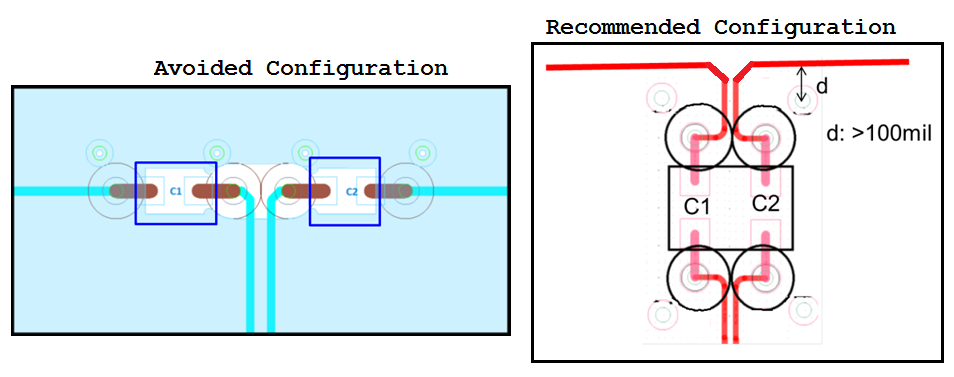

What to Avoid for AC Capacitor Configuration

The differential signal vias must be coupled to reduce the inductance for each individual signal via. Intel recommends tightly-coupled AC capacitors over single-ended AC capacitor placement.

Figure 50. Avoided vs Recommended AC Capacitor Layout Configuration Comparison