A newer version of this document is available. Customers should click here to go to the newest version.

1. About the Nios® V Embedded Processor

2. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Software and Platform Designer

3. Nios® V Processor Software System Design

4. Nios® V Processor Configuration and Booting Solutions

5. Nios® V Processor - Using the MicroC/TCP-IP Stack

6. Nios® V Processor Debugging, Verifying, and Simulating

7. Nios® V Processor — Remote System Update

8. Nios® V Processor — Using Custom Instruction

9. Nios® V Embedded Processor Design Handbook Archives

10. Document Revision History for the Nios® V Embedded Processor Design Handbook

4.1. Introduction

4.2. Linking Applications

4.3. Nios® V Processor Booting Methods

4.4. Introduction to Nios® V Processor Booting Methods

4.5. Nios® V Processor Booting from Configuration QSPI Flash

4.6. Nios® V Processor Booting from On-Chip Memory (OCRAM)

4.7. Nios® V Processor Booting from Tightly Coupled Memory (TCM)

4.8. Summary of Nios® V Processor Vector Configuration and BSP Settings

6.5.1. Prerequisites

6.5.2. Setting Up and Generating Your Simulation Environment in Platform Designer

6.5.3. Creating Nios V Processor Software

6.5.4. Generating Memory Initialization File

6.5.5. Generating System Simulation Files

6.5.6. Running Simulation in the QuestaSim Simulator Using Command Line

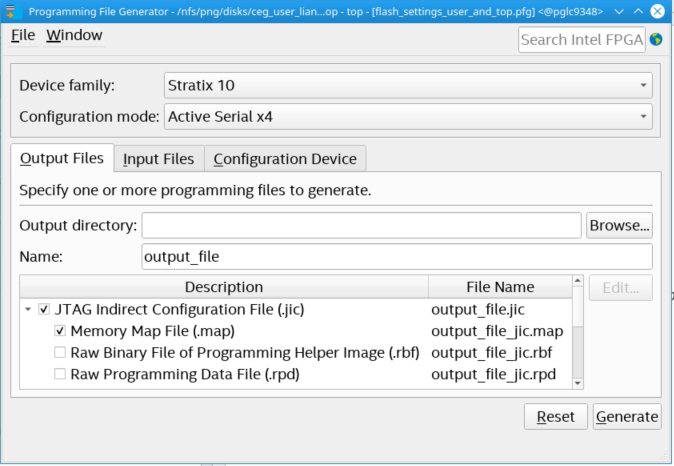

4.5.2.1.5. Programming Files Generation

- Go to File > Programming File Generator.

- Select the Configuration mode to be Active Serial x4.

- In the Output Files tab, select JTAG Indirect Configuration File (.jic).

Figure 67. Programming File Generator (Output Files)

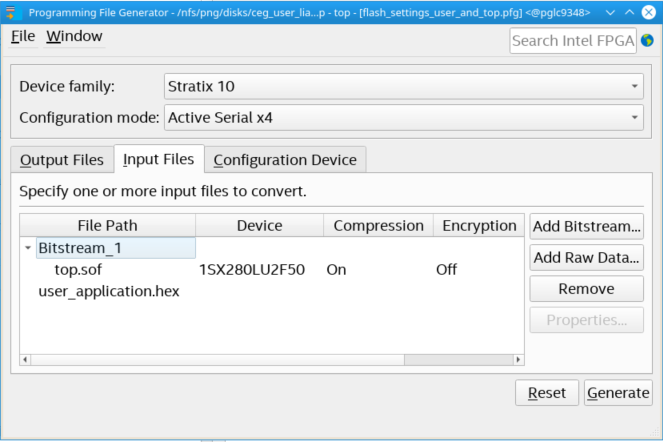

- In the Input Files tab, perform the following steps:

- Add the SOF file by clicking Add Bitstream.

- Add the user application (.hex) file by clicking Add Raw Data.

- Select the HEX file and click Properties.

- Select Bit Swap : On.

Figure 68. Programming File Generator (Input Files)

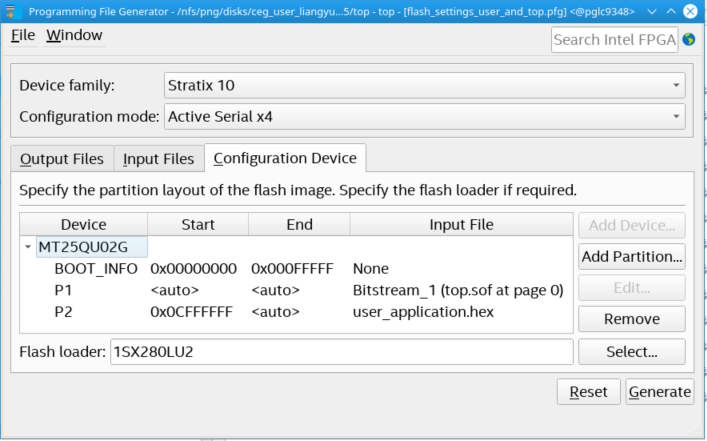

- In the Configuration Device tab,

- Add the flash device by clicking Add Device.

- If you are using a supported device, you may make your selection, and click OK. Else, proceed to Apply the Configuration Device window.

- Add the SOF file by selecting the flash device and click Add Partition.

- Add the user application (.hex) file by selecting the flash device and click Add Partition. Select the Address Mode to Start and set the Start address to the value set for PAYLOAD_OFFSET in mailbox_bootcopier.c.

- Select the Flash loader according to the Intel FPGA device.

Figure 69. Programming File Generator (Configuration Device)

- Add the flash device by clicking Add Device.

- Click Generate to generate the JIC file.

Applying the Configuration Device Window

The Configuration Device allows for choosing a specific supported device or alternatively an unsupported device.

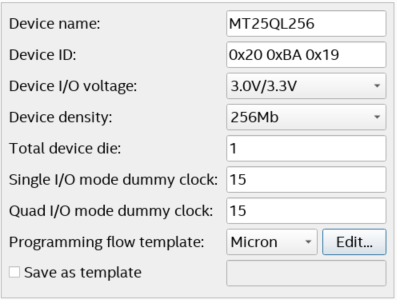

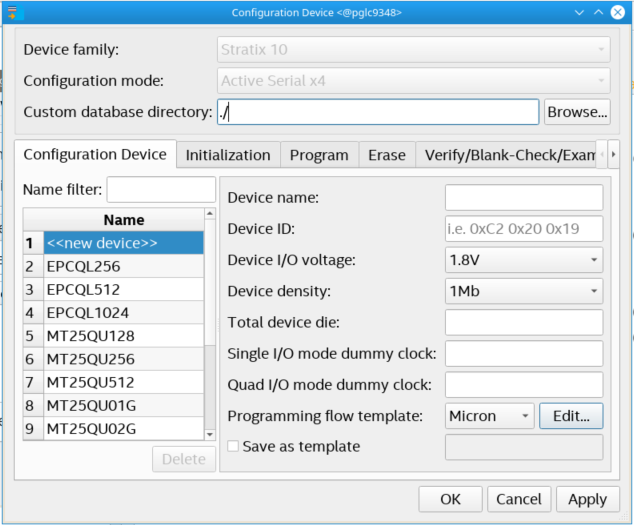

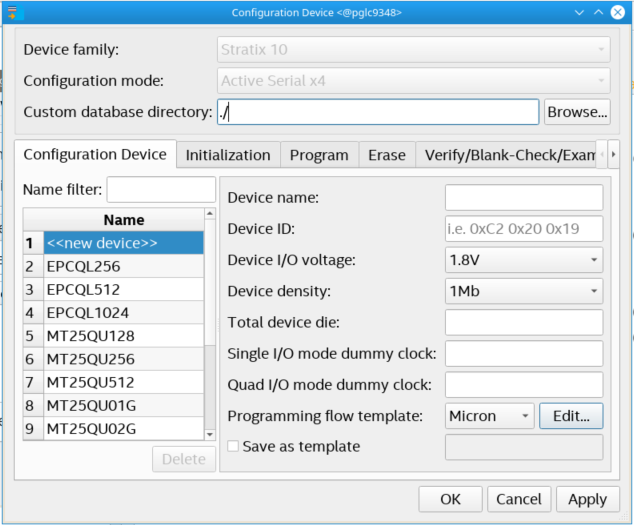

Figure 70. Configuration Device Window

- If you are using a supported device, make your selection, and click OK. Else, proceed with the following steps:

- Select <<new device>>.

- Enter the information about Device name, Device ID, Device I/O voltage, Device density, Total device die, Dummy clock (Single I/O or Quad I/O mode) and Programming flow template.

- Click Apply.

Note: The Programming flow template helps you to define a template for flash operation in Initialization, Program, Erase, Verify/Blank-Check/Examine and Termination. If the device is not available for selection, refer to Modifying Programming Flows in Generic Flash Programmer User Guide to modify the programming flow.