A newer version of this document is available. Customers should click here to go to the newest version.

1. About this Document

2. Introduction

3. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Pro Edition and Platform Designer

4. Nios® V Processor Software System Design

5. Nios® V Processor Configuration and Booting Solutions

6. Nios® V Processor - Using the MicroC/TCP-IP Stack

7. Nios® V Processor Debugging, Verifying, and Simulating

8. Document Revision History for the Nios® V Embedded Processor Design Handbook

5.1. Introduction

5.2. Linking Applications

5.3. Nios® V Processor Booting Methods

5.4. Introduction to Nios® V Processor Booting Methods

5.5. Nios® V Processor Booting from Configuration QSPI Flash

5.6. Nios V Processor Booting from On-Chip Memory (OCRAM)

5.7. Summary of Nios V Processor Vector Configuration and BSP Settings

7.4.1. Prerequisites

7.4.2. Setting Up and Generating Your Simulation Environment in Platform Designer

7.4.3. Creating Nios V Processor Software

7.4.4. Generating Memory Initialization File

7.4.5. Generating System Simulation Files

7.4.6. Running Simulation in the QuestaSim Simulator Using Command Line

2.3.4. Programming Nios® V/m into the FPGA Device

To program Nios® V/m processor based system into the FPGA and to run your application, use Intel Quartus Programmer tool.

- To create the Nios® V/m processor inside the FPGA device, download the .sof file onto the board with the following command.

Windows:

quartus_pgm -c 1 -m JTAG -o p;top.sof@1Linux:quartus_pgm -c 1 -m JTAG -o p\;top.sof@1Note:- -c 1 is referring to cable number connected to the Host Computer.

- @1 is referring to device index on the JTAG Chain and may differ for your board.

- Download the .elf using the niosv-download command.

niosv-download <elf file>Note: Set the Enable Debug option to use niosv-download command. - To run the Hello World application program, reset the Nios® V/m processor system using the toggle_issp.tcl script.

quartus_stp -t toggle_issp.tcl - Use the JTAG UART terminal to print the stdout and stderr of the Nios® V/m processor system.

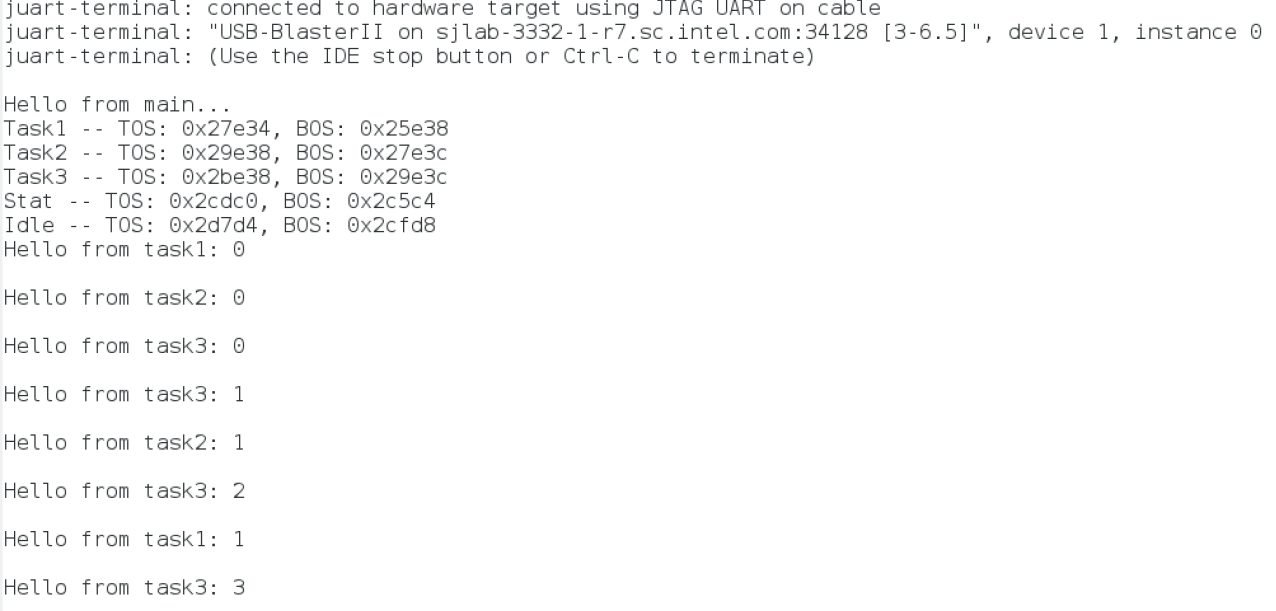

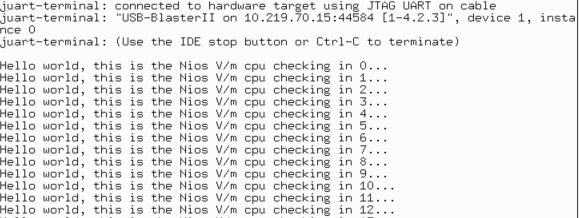

juart-terminal - The Hello World application displays as shown in the following figures.

Figure 6. Output of the Hello World application using hello.c

Figure 7. Output of the Hello World application using hello_ucosii.c

Figure 7. Output of the Hello World application using hello_ucosii.c