Intel® Quartus® Prime Pro Edition User Guide: Debug Tools

A newer version of this document is available. Customers should click here to go to the newest version.

2.4.1. Preserving Signals for Monitoring and Debugging

To ensure that specific nodes in your RTL are available for Signal Tap debugging after synthesis and place-and-route, you can apply the preserve_for_debug attribute to the signals of interest in your RTL, and also specify the Enable preserve for debug assignments project .qsf setting. Refer to .qsf syntax in Table 9.

When you preserve signals using this technique, the Compiler generates the Preserve for Debug Assignments report following synthesis that shows the status and name of all nodes with the preserve_for_debug attribute in your RTL.

Follow these steps to preserve signals for monitoring and debugging:

- In your design RTL, mark signals that you want to preserve with the preserve_for_debug attribute:

Figure 28. preserve_for_debug Attribute

- Open the project containing Signal Tap in the Intel® Quartus® Prime software and perform one of the following:

- To enable preservation and reporting for specific instances, click Assignments > Assignment Editor, and then specify the Enable preserve for debug assignments assignment To any instance of interest.

Or

- To enable preservation and reporting project-wide, in Assignments > Settings > Signal Tap Logic Analyzer, turn on Enable preserve for debug assignments.1

- To enable preservation and reporting for specific instances, click Assignments > Assignment Editor, and then specify the Enable preserve for debug assignments assignment To any instance of interest.

- To synthesize the design, on the Compilation Dashboard, click Analysis & Synthesis. The Compilation Report appears when synthesis is complete.

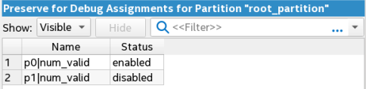

- To view the results of signal preservation, open the Preserve for Debug Assignments report located in the Synthesis > Partition <name> > Preserve for Debug report folder.

Figure 29. Preserve for Debug Assignments Report

- Run full compilation to perform place and route of the design and Signal Tap instance, as Step 3: Compile the Design and Signal Tap Instances describes. The debug signals that you preserve in step 2 persist through the Fitter into the finalized compilation database.

- Optionally, make some incremental changes to the Signal Tap configuration without running full recompilation, as Changing the Post-Fit Signal Tap Target Nodes describes.

| Method | Description | Example |

|---|---|---|

| preserve_for_debug_enable | Set this assignment to On to preserve any nodes or hierarchies marked with preserve_for_debug. If set to Off or not used, any preserve_for_debug assignments are ignored. Use this as a quick way to disable all debug node preservation when optimizing a completed design. The Compiler reports these nodes in the Preserve for Debug Assignments report following compilation. | set_instance_assignment -name PRESERVE_FOR_DEBUG_ENABLE ON |

| preserve_for_debug (Enable preserve for debug assignments in the Assignment Editor) |

Instance-specific .qsf assignment that overrides the global assignment and enables preservation of all types of nodes through synthesis post-synthesis or post-fit debugging purposes. When On, this assignment enables preservation for the hierarchy that you specify. You can enable or disable this with the Preserve signal for debug assignment in the Assignment Editor. The Compiler reports these nodes in the Preserve for Debug Assignments report following compilation. | set_instance_assignment -name PRESERVE_FOR_DEBUG ON -to <node hpath> |