DQS Read Operation

Data validation is done by comparing data received by the ALTDQ_DQS2 core (read_data_out) against the content of the check_fifo.

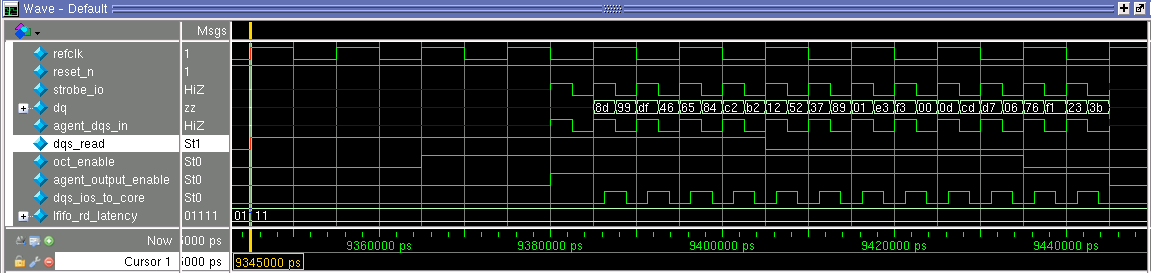

DQS read is initiated by the DQS driver when dqs_read is asserted at 9.345 ms. The lfifo_rdata_en_full (dqs_read) of the ALTDQ_DQS2 IP core is also asserted for the entire length of the desired read burst, which in this case is 12 full-rate cycles. As the DQS agent receive the read command, it is then ready to sends out data as per requested. This is shown with agent_output_enable being asserted from 9.380 ms to 9.445 ms. During this period, the DQS agent drives the strobe and data lines of the external memory interface. In this test bench, strobe_io is driven by dqs_agent_to_ios. When output enable is deasserted, strobe_io will be set to Hi-Z.

As the incoming data arrives at the ALTDQ_DQS2 IP core, the edge-aligned data on read_write_data_io, and strobe on strobe_io ports. Following will discuss how the data is captured in the FPGA before it is made available in the core.