Analyzing Same Edge Transfer

The following set_false_path commands ensure that you are analyzing only the same edge transfers, by removing the opposite edge transfers. Using multicycle commands ensure that the analysis is done on the correct transfer cycle.

set_false_path Commands

set_false_path -setup -rise_from [get_clocks {virtual_dqs_in}] -fall_to [get_clocks {dqs_in}]

set_false_path -setup -fall_from [get_clocks {virtual_dqs_in}] -rise_to [get_clocks {dqs_in}]

set_false_path -hold -rise_from [get_clocks {virtual_dqs_in}] -rise_to [get_clocks {dqs_in}]

set_false_path -hold -fall_from [get_clocks {virtual_dqs_in}] -fall_to [get_clocks {dqs_in}]

set_multicycle_path Commands

set_multicycle_path -rise_from [get_clocks {virtual_dqs_in}] -rise_to [get_clocks {dqs_in}] -setup -end 0

set_multicycle_path -fall_from [get_clocks {virtual_dqs_in}] -fall_to [get_clocks {dqs_in}] -setup -end 0

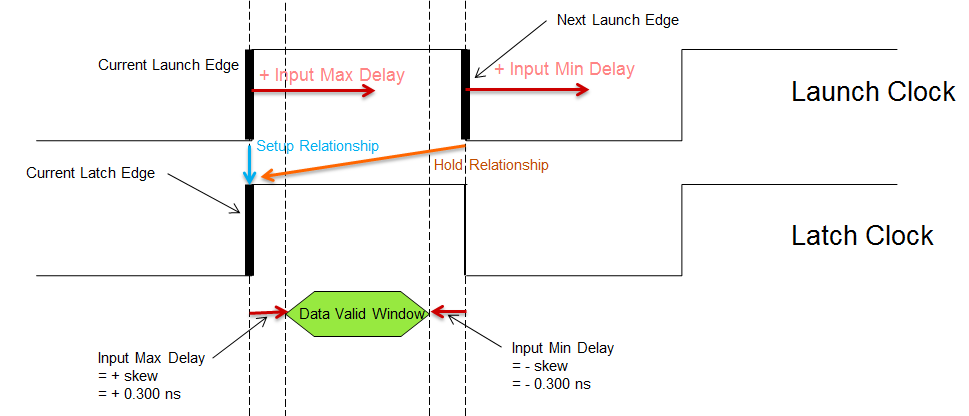

set_input_delay Commands

set_input_delay -clock {virtual_dqs_in} -max -add_delay 0.300 [get_ports{read_write_data_io[*]}]

set_input_delay -clock{virtual_dqs_in} -min -add_delay -0.300 [get_ports{read_write_data_io[*]}]

set_input_delay -clock {virtual_dqs_in} -clock_fall -max -add_delay 0.300 [get_ports{read_write_data_io[*]}]

set_input_delay -clock{virtual_dqs_in} -clock_fall -min -add_delay -0.300 [get_ports{read_write_data_io[*]}]