Multi Channel DMA Intel® FPGA IP for PCI Express User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

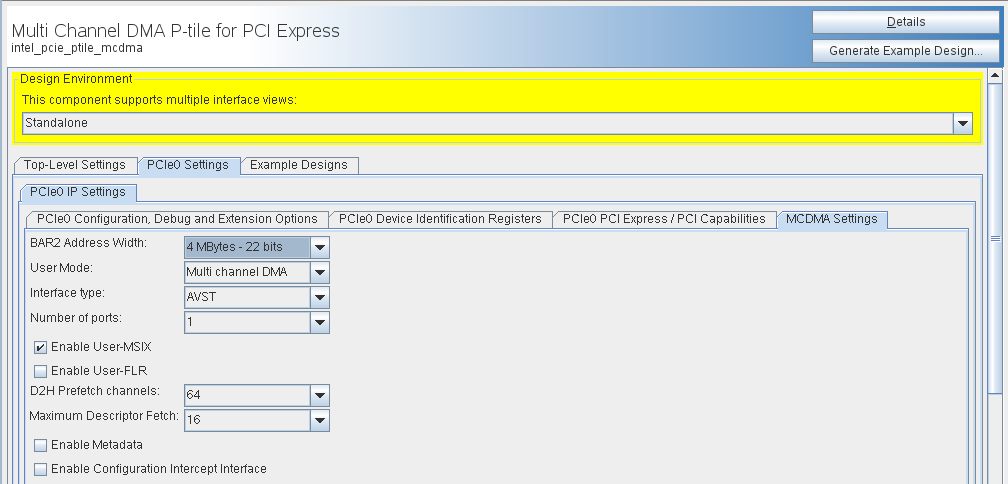

6.2.5. MCDMA Settings

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| BAR2 Address Width |

128 Bytes - 8 Bytes |

4 Mbytes – 22 bits |

Address width for PIO AVMM port. Default address width is 22 bits |

| User Mode |

Multi channel DMA Bursting Master Bursting Slave BAM-BAS BAM-MCDMA |

Multi channel DMA |

This option allows user to configure the mode of operation for MCDMA IP. MCDMA mode has the DMA functionality. BAM and BAS offer Bursting Master and Slave AVMM capabilities without DMA functionality |

| Interface type |

AVMM AVST |

AVMM |

User logic interface type for D2HDM and H2DDM. Default: Avalon-MM Interface |

| Number of ports |

1 4 |

1 |

If Interface Type = AVMM, Value =1 If Interface Type = AVST, Value= 1 or 4 |

| Enable User-MSIX |

On / Off |

Off |

User MSI-X is enables user application to initiate interrupts through MCDMA, this option is available only if the user selects MCDMA mode |

| Enable User-FLR |

On / Off |

Off |

User FLR, interface allows passing of FLR signals to the user side application |

| D2H Prefetch channels |

8 16 32 64 128 256 |

8 |

Sets the D2H Prefetch channels

For AVST options are 8,16,32,64

Note: This parameter is not available for configuration in Intel® Quartus® Prime 21.3

Note: This parameter is not applicable for AVMM

.

|

| Maximum Descriptor Fetch |

16 32 64 |

16 |

Sets the maximum descriptors that are fetched per D2H prefetch channel.

Note: This parameter is not available for configuration in AVMM interface type

|

| Enable Metadata |

On / Off |

Off |

Enables Metadata

Note: This parameter is only available when the Interface Type is set to AVST.

|

| Enable Configuration Intercept Interface |

On / Off |

Off |

Select to enable configuration intercept interface. |