AXI Multichannel DMA Intel® FPGA IP for PCI Express* User Guide

ID

817911

Date

7/22/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

4.4.1. PCIe AXI-ST TX Interface (ss_tx_st)

4.4.2. PCIe AXI-ST RX Interface (ss_rx_st)

4.4.3. Control and Status Register Interface (ss_csr_lite)

4.4.4. Flow Control Credit Interface

4.4.5. Configuration Intercept Interface (CII)

4.4.6. Completion Timeout Interface (ss_cplto)

4.4.7. Function Level Reset Interface

4.4.8. Control Shadow Interface (ss_ctrlshadow)

4.5.1. H2D AXI-ST Source (h2d_st_initatr)

4.5.2. D2H AXI-ST Sink (d2h_st_respndr)

4.5.3. BAM AXI-MM Master (bam_mm_initatr)

4.5.4. BAS AXI-MM Slave (bas_mm_respndr)

4.5.5. PIO AXI-Lite Master (pio_lite_initiatr)

4.5.6. HIP Reconfig AXI-Lite Slave (user_csr_lite)

4.5.7. User Event MSI-X (user_msix)

4.5.8. User Event MSI (user_msi)

4.5.9. User Function Level Reset (user_flr)

4.5.10. User Configuration Intercept Interface - EP Only

4.5.11. Configuration Slave (cs_lite_respndr) - RP Only

6.4.2. Generating the Design Example

Using Quartus® Prime, you can generate a design example for the AXI Multichannel DMA IP.

Figure 24. Design Example Generation

Following is the procedure to generate a design example:

- In the Quartus® Prime Pro Edition software, create a new project by clicking File > New Project Wizard. Click Next.

- Specify the Directory, Name, and Top-Level Entity. Click Next.

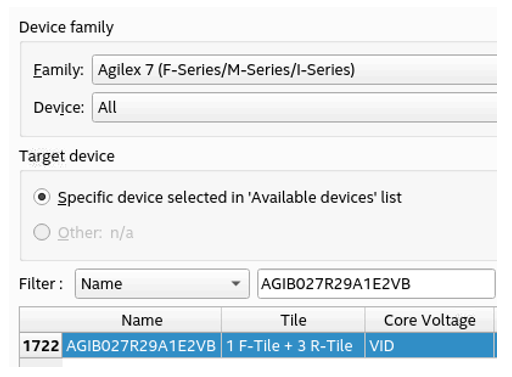

- Specify the Family, Device & Board Settings as follows:

- Select Family: Agilex™ 7 (F-Series/M-Series/I-Series).

- Select Target device: Filter (Name): AGIB027R29A1E2VB.

- Click the target device in the table.

Note: The device used for the Quartus® Prime-generated design example matches the device used in the target FPGA development kit board and may not be the same as the target device selected here.Figure 25. Selecting Device Family and Target Device

- Click Finish.

- In the IP Catalog pane, type PCI in the Filter, and select AXI Multichannel DMA Intel FPGA IP for PCI Express under Interface Protocols > PCI Express. Click + Add....

- In the New IP Variant dialogue box, specify the file name. Click Create.

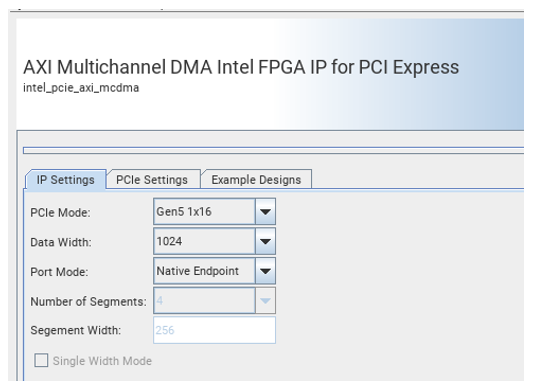

- Configure the IP parameters if needed in the IP Settings and PCIe Settings tabs.

Figure 26. IP Parameter Editor

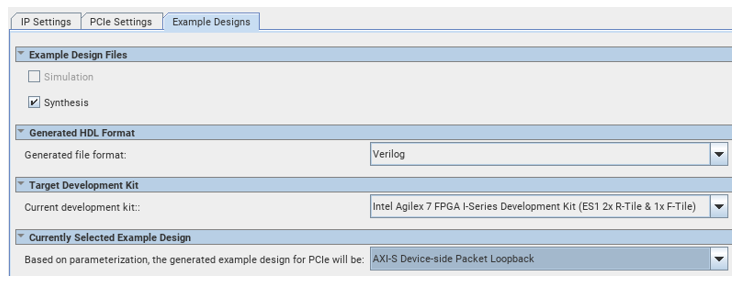

- Go to the Example Designs tab. Select Current Development Kit, Example Design and click Generate Example Design.

Note: The current release does not support design example simulation.Figure 27. Design Example Tab

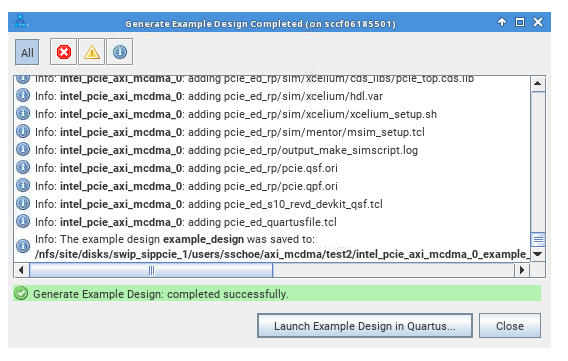

- After the design example generation is completed, click Launch Example Design in Quartus.

Figure 28. Launch Design Example

- In Quartus® Prime, click Processing > Start Compilation to compile the design example and generate the bitstream (.sof) file.