AXI Multichannel DMA Intel® FPGA IP for PCI Express* User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

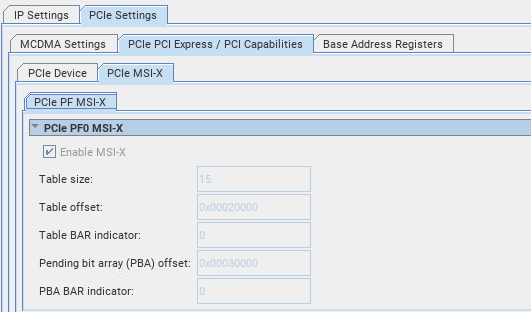

5.2.2.2.1. PCIe PF MSI-X

The PF MSI-X capability parameters in Multichannel DMA, BAM+MCDMA and BAM+BAS+MCDMA modes are automatically set and cannot be modified.

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Enable MSI-X | On / Off | See Description | Enables or disables the MSI-X capability.

Note: In Multichannel DMA, BAM+MCDMA and BAM+BAS+MCDMA user modes, the MSI-X capability is automatically enabled and capability register are set by the IP GUI. You cannot modify the capability register values.

|

| Table Size | 0 - 2047 | 15 | Sets the number of entries in the MSI-X table System software reads this field to determine the MSI-X table size N, which is encoded as N-1 |

| Table offset | 0x00020000 | 0x00020000 | Sets the read-only base address of the MSI-X table Points to the base of the MSI-X table. The lower 3 bits of the table BAR indicator (BIR) are set to zero by software to form a 64-bit qword-aligned offset |

| Table BAR Indicator | 0 | 0 | Specifies which one of a function's base address registers, located beginning at 0x10 in the Configuration Space, maps the MSI-X table into memory space This field is read-only |

| Pending bit array (PBA) offset | 0x00030000 | 0x00030000 | Used as an offset from the address contained in one of the function's Base Address registers to point to the base of the MSI-X PBA The lower 3 bits of the PBA BIR are set to zero by software to form a 32-bit qword-aligned offset. This field is read-only after being programmed |

| PBA BAR Indicator | 0 | 0 | Specifies the function Base Address registers, located beginning at 0x10 in Configuration Space, that maps the MSI-X PBA into memory space This field is read-only in the MSI-X Capability Structure |