AXI Multichannel DMA Intel® FPGA IP for PCI Express* User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

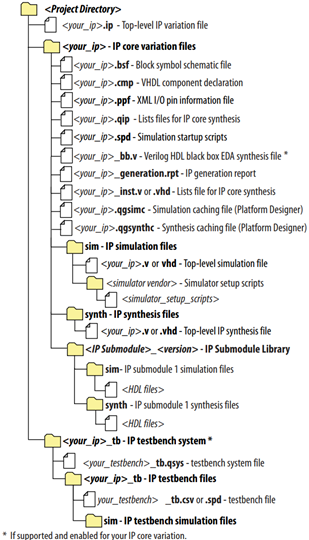

6.2. IP Core Generation Output

The Quartus® Prime Pro Edition software generates the following output file structure for individual IP cores that are not part of a Platform Designer system.

| File Name | Description |

|---|---|

| <your_ip>.ip | Top-level IP variation file that contains the parameterization of an IP core in your project. If the IP variation is part of a Platform Designer system, the parameter editor also generates a .qsys file. |

| <your_ip>.cmp | The VHDL Component Declaration (.cmp) file is a text file that contains local generic and port definitions that you use in VHDL design files. |

| <your_ip>_generation.rpt | IP or Platform Designer generation log file. Displays a summary of the messages during IP generation. |

| <your_ip>.qgsimc (Platform Designer systems only) | Simulation caching file that compares the .qsys and .ip files with the current parameterization of the Platform Designer system and IP core. This comparison determines if Platform Designer can skip regeneration of the HDL |

| <your_ip>.qgsynth (Platform Designer systems only) | Synthesis caching file that compares the .qsys and .ip files with the current parameterization of the Platform Designer system and IP core. This comparison determines if Platform Designer can skip regeneration of the HDL. |

| <your_ip>.qip | Contains all information to integrate and compile the IP component. |

| <your_ip>.csv | Contains information about the upgrade status of the IP component. |

| <your_ip>.bsf | A symbol representation of the IP variation for use in Block Diagram Files (.bdf). |

| <your_ip>.spd | Input file that ip-make-simscript requires to generate simulation scripts. The .spd file contains a list of files you generate for simulation, along with information about memories that you initialize. |

| <your_ip>.ppf | The Pin Planner File (.ppf) stores the port and node assignments for IP components you create for use with the Pin Planner. |

| <your_ip>_bb.v | Use the Verilog blackbox (_bb.v) file as an empty module declaration for use as a blackbox. |

| <your_ip>_inst.v or <your_ip>_inst.vhd |

HDL example instantiation template. Copy and paste the contents of this file into your HDL file to instantiate the IP variation. |

| <your_ip>.regmap | If the IP contains register information, the Quartus® Prime Software generates the .regmap file. The .regmap file describes the register map information of master and slave interfaces. This file complements the .sopcinfo file by providing more detailed register information about the system. This file enables register display views and user customizable statistics in System Console. |

| <your_ip>.svd | Allows HPS System Debug tools to view the register maps of peripherals that connect to HPS within a Platform Designer system. During synthesis, the Quartus® Prime Software stores the .svd files for slave interface visible to the System Console masters in the .sof file in the debug session. System Console reads this section, which Platform Designer queries for register map information. For system slaves, Platform Designer accesses the registers by name. |

| <your_ip>.v <your_ip>.vhd |

HDL files that instantiate each submodule or child IP core for synthesis or simulation. |

| /mentor/ | Contains a msim_setup.tcl script to set up and run a ModelSim® simulation. |

| /aldec/ | Contains a Riviera-PRO* script rivierapro_setup.tcl to setup and run a simulation. |

| /synopsys/vcs/ /synopsys/vcsmx/ |

Contains a shell script vcs_setup.sh to set up and run a VCS* simulation. Contains a shell script vcsmx_setup.sh and synopsys_sim.setup file to set up and run a VCS* MX simulation. |

| /cadence/ | Contains a shell script ncsim_setup.sh and other setup files to set up and run an NCSim simulation. |

| /submodules/ | Contains HDL files for the IP core submodule. |

| /<IP submodule>/ | Platform Designer generates /synth and /sim sub-directories for each IP submodule directory that Platform Designer generates. |