AXI Multichannel DMA Intel® FPGA IP for PCI Express* User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

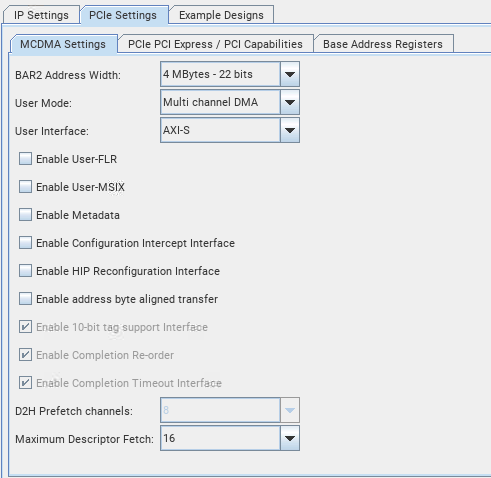

5.2.1.1. Multichannel DMA Mode

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| BAR2 Address Width | 128 Bytes – 7 bits . . . 8 EBytes – 63 bits |

4 Mbytes – 22 bits | Sets the BAR2 size used for PIO functionality.

Note: This parameter is available only in Multichannel DMA user mode.

|

| User Mode | Multichannel DMA Bursting Master Bursting Slave BAM+BAS BAM+MCDMA BAM+BAS+MCDMA |

Multichannel DMA |

This parameter allows you to configure the mode of operation for the user application:

|

| User Interface | AXI-S |

AXI-S | Sets the type of DMA user interface. Currently AXI Stream interface is supported. |

| Enable User-FLR | On / Off | Off | Select to enable User FLR interface which allows passing of FLR signals to the user side application.

Note: User FLR is not supported in Bursting Master, Bursting Slave, and BAM+BAS modes.

|

| Enable User-MSIX | On / Off | Off | User MSI-X interface enables the user application to initiate interrupts through the MCDMA IP.

Note: User MSI-X is not supported in Bursting Master, Bursting Slave, and BAM+BAS modes.

|

| Enable Metadata | On / Off | Off | Enables or disables 8-byte metadata. Metadata is the 8-byte user application data that is transferred to and from the device via the DEST address field (for H2D DMA) and SRC address field (for D2H DMA) in the AXI Streaming mode. |

| Enable Configuration Intercept Interface | On / Off | Off | Select to enable user configuration intercept interface. |

| Enable HIP Reconfiguration Interface | On / Off | Off | Select to enable Hard IP reconfiguration interface. |

| Enable address byte aligned transfer | On / Off | Off | This option enables the Byte aligned address mode support needed for Kernel or DPDK drivers. The DMA makes no assumption on the alignment of data w.r.t to address. |

| Enable 10-bit tag support interface | On | On | Enables 10-bit tag support interface |

| Enable Completion Re-order | On | On | Enables completion re-order |

| Enable Completion Timeout Interface | On | On | Enables completion timeout interface |

| D2H Prefetch channels | 8 16 32 64 128 256 512 |

8 | Sets the number of D2H prefetch channels for the AXI-S interface type. IP Parameter Editor automatically selects the value based on the DMA channel count. |

| Maximum Descriptor Fetch | 16 32 64 |

16 | Sets the maximum descriptors that are fetched per D2H prefetch channel. Applicable to the AXI-S interface type. |