External Memory Interfaces (EMIF) IP User Guide: Agilex™ 5 FPGAs and SoCs

ID

817467

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Agilex™ 5 FPGA IP

2. Agilex™ 5 FPGA EMIF IP – Introduction

3. Agilex™ 5 FPGA EMIF IP – Product Architecture

4. Agilex™ 5 FPGA EMIF IP – End-User Signals

5. Agilex™ 5 FPGA EMIF IP – Simulating Memory IP

6. Intel® Agilex™ 5 FPGA EMIF IP - DDR4 Support

7. Intel® Agilex™ 5 FPGA EMIF IP - LPDDR4 Support

8. Intel® Agilex™ 5 FPGA EMIF IP - LPDDR5 Support

9. Agilex™ 5 FPGA EMIF IP – Timing Closure

10. Agilex™ 5 FPGA EMIF IP – Controller Optimization

11. Agilex™ 5 FPGA EMIF IP – Debugging

12. Document Revision History for External Memory Interfaces (EMIF) IP User Guide

3.2.1. Agilex™ 5 EMIF Architecture: I/O Subsystem

3.2.2. Agilex™ 5 EMIF Architecture: I/O SSM

3.2.3. Agilex™ 5 EMIF Architecture: HSIO Bank

3.2.4. Agilex™ 5 EMIF Architecture: I/O Lane

3.2.5. Agilex™ 5 EMIF Architecture: Input DQS Clock Tree

3.2.6. Agilex™ 5 EMIF Architecture: PHY Clock Tree

3.2.7. Agilex™ 5 EMIF Architecture: PLL Reference Clock Networks

3.2.8. Agilex™ 5 EMIF Architecture: Clock Phase Alignment

3.2.9. User Clock in Different Core Access Modes

6.4.3.1. 1 Rank x 8 Discrete (Memory Down) Topology

6.4.3.2. 1 Rank x 16 Discrete (Memory Down) Topology

6.4.3.3. VREF_CA/RESET Signal Routing Guidelines for 1 Rank x 8 and 1 Rank x 16 Discrete (Memory Down) Topology

6.4.3.4. Skew Matching Guidelines for DDR4 (Memory Down) Discrete Configurations

6.4.3.5. Power Delivery Recommendation for DDR4 Discrete Configurations

6.4.3.6. DDR4 Simulation Strategy

11.1. Interface Configuration Performance Issues

11.2. Functional Issue Evaluation

11.3. Timing Issue Characteristics

11.4. Verifying Memory IP Using the Signal Tap Logic Analyzer

11.5. Generating Traffic with the Test Engine IP

11.6. Guidelines for Developing HDL for Traffic Generator

11.7. Hardware Debugging Guidelines

11.8. Create a Simplified Design that Demonstrates the Same Issue

11.9. Measure Power Distribution Network

11.10. Measure Signal Integrity and Setup and Hold Margin

11.11. Vary Voltage

11.12. Operate at a Lower Speed

11.13. Determine Whether the Issue Exists in Previous Versions of Software

11.14. Determine Whether the Issue Exists in the Current Version of Software

11.15. Try A Different PCB

11.16. Try Other Configurations

11.17. Debugging Checklist

11.18. Categorizing Hardware Issues

11.19. Signal Integrity Issues

11.20. Characteristics of Signal Integrity Issues

11.21. Evaluating Signal Integrity Issues

11.22. Skew

11.23. Crosstalk

11.24. Power System

11.25. Clock Signals

11.26. Address and Command Signals

11.27. Read Data Valid Window and Eye Diagram

11.28. Write Data Valid Window and Eye Diagram

11.29. Hardware and Calibration Issues

11.30. Memory Timing Parameter Evaluation

11.31. Verify that the Board Has the Correct Memory Component or DIMM Installed

7.2.1.2. LPDDR4 Component Options

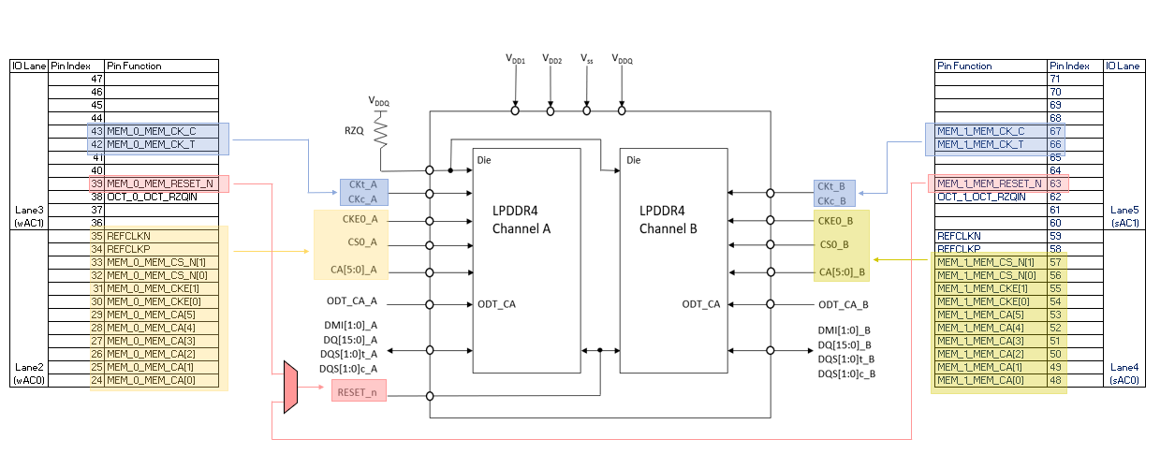

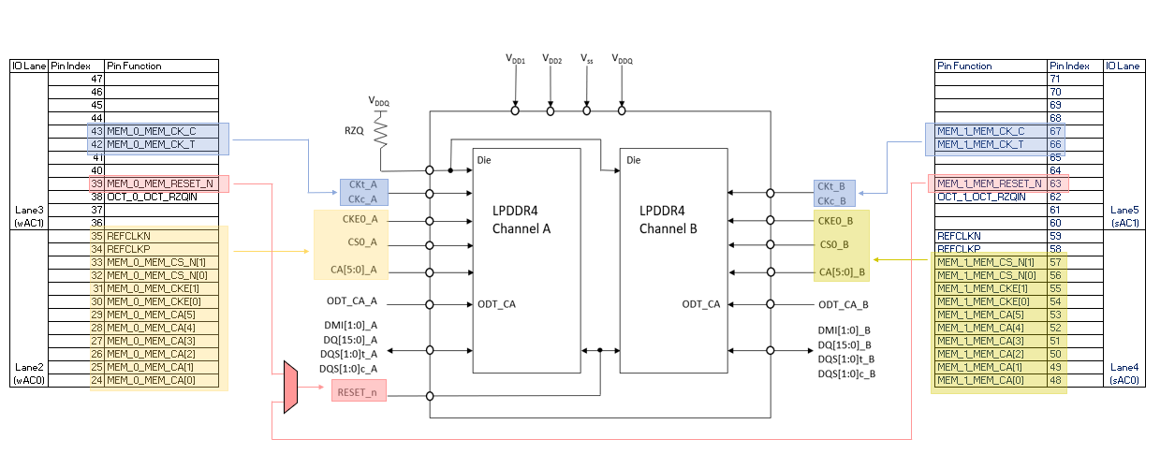

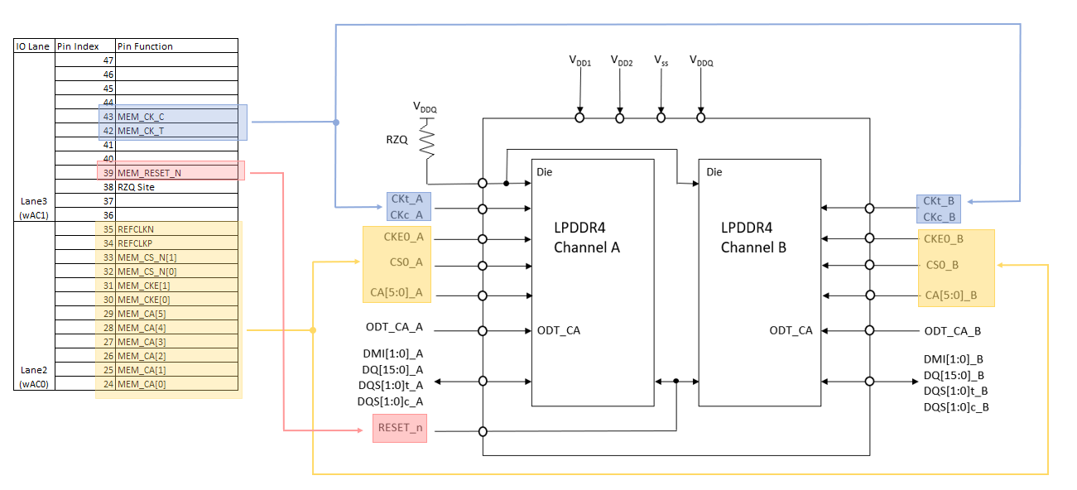

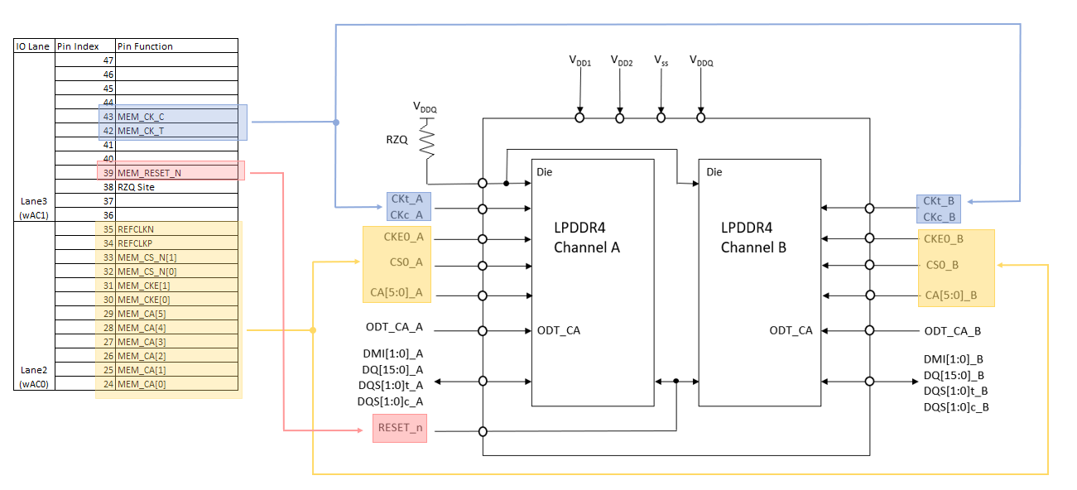

The table and figure below illustrate the pin placement and routing recommendation for a single 32-bit channel, and two 16-bit channels, respectively.

Note: Always consult your memory vendor’s data sheet to verify pin placement and routing plans.

| Pins | 1 CH x32 | 2 CH x16 | |

|---|---|---|---|

| Data | DQ[15:0]_A DQ[15:0]_B |

DQ[15:0]_A |

DQ[15:0]_B |

| Data mask | DMI[1:0]_A DMI[1:0]_B |

DMI[1:0]_A |

DMI[1:0]_B |

| Data strobe | DQS[1:0]_t_A DQS[1:0]_c_A DQS[1:0]_t_B DQS[1:0]_t_B |

DQS[1:0]_t_A DQS[1:0]_c_A |

DQS[1:0]_t_B DQS[1:0]_c_B |

| Address/Command | CA[5:0]_A CS0_A CA[5:0]_B CS0_B |

CA[5:0]_A CS0_A |

CA[5:0]_B CS0_B |

| Clock | CK_t_A CK_c_A CK_t_B CK_c_B |

CK_t_A CK_c_A |

CK_t_B CK_c_B |

| Reset | RESET_n |

RESET_n (Resistor jumper to select from mem_0 or mem_1.) |

|

| Clock Enable | CKE | CKE | |

Figure 29. Single-Channel x32 LPDDR4, Single Rank

Figure 30. Dual-Channel x16 LPDDR4, Single Rank