AN 847: Signal Tap Tutorial with Design Block Reuse: for Intel® Arria® 10 FPGA Development Board

ID

683712

Date

12/21/2020

Public

1. Introduction

2. Core Partition Reuse Debug—Developer

3. Core Partition Reuse Debug—Consumer

4. Root Partition Reuse Debug—Developer

5. Root Partition Reuse Debug—Consumer

6. AN 847: Signal Tap Tutorial with Design Block Reuse for Intel® Arria® 10 FPGA Development Board Archives

7. Document Revision History for AN 847: Signal Tap Tutorial with Design Block Reuse for Intel® Arria® 10 FPGA Development Board

2.1. Step 1: Creating a Core Partition

2.2. Step 2: Creating Partition Boundary Ports

2.3. Step 3: Compiling and Checking Debug Nodes

2.4. Step 4: Exporting the Core Partition and Creating the Black Box File

2.5. Step 5: Copying Files to Consumer Project

2.6. Step 6: Creating a Signal Tap File (Optional)

2.7. Step 7: Programming the Device and Verifying the Hardware

2.8. Step 8: Verifying Hardware with Signal Tap

3.1. Step 1: Adding Files and Running Synthesis

3.2. Step 2: Creating a Signal Tap File

3.3. Step 3: Creating a Partition for blinking_led_top

3.4. Step 4: Compiling the Design and Verifying Debug Nodes

3.5. Step 5: Programming the Device and Verifying the Hardware

3.6. Step 6: Verifying Hardware with Signal Tap

4.1. Step 1: Creating a Reserved Core Partition and Defining a Logic Lock Region

4.2. Step 2: Generating and Instantiating SLD JTAG Bridge Agent in the Root Partition

4.3. Step 3: Generating and Instantiating the SLD JTAG Bridge Host

4.4. Step 4: Generating HDL Instance of Signal Tap

4.5. Step 5: Compiling Export Root Partition and Copying Files to Consumer Project

4.6. Step 6: Programming the Device and Verifying the Hardware

4.7. Step 7: Generating a Signal Tap File for the Root Partition

4.8. Step 8: Verifying the Hardware with Signal Tap

5.1. Step 1: Adding Files to Customer Project

5.2. Step 2: Generating and Instantiating SLD JTAG Bridge Host in Reserved Core Partition

5.3. Step 3: Synthesizing, Creating Signal Tap File, and Compiling

5.4. Step 4: Programming the Device and Verifying the Hardware

5.5. Step 5: Verifying the Hardware of Reserved Core Partition with Signal Tap

5.6. Step 6: Verifying Hardware of Root Partition with Signal Tap

3.2. Step 2: Creating a Signal Tap File

Create a Signal Tap file that includes partition boundary ports from the reused core partition.

- Click Tools > Signal Tap Logic Analyzer.

- In the Signal Tap logic analyzer GUI, click auto_signaltap_0.

- In the Setup tab, double-click to launch the Node Finder.

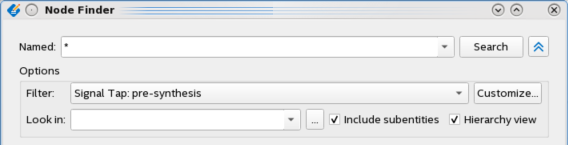

- In the Node Finder, type * in the Named field, set Filter to Signal Tap: pre-synthesis, and then click Search.

Figure 27. Node Finder Search

The Matching Nodes list shows signals that match the search criteria.

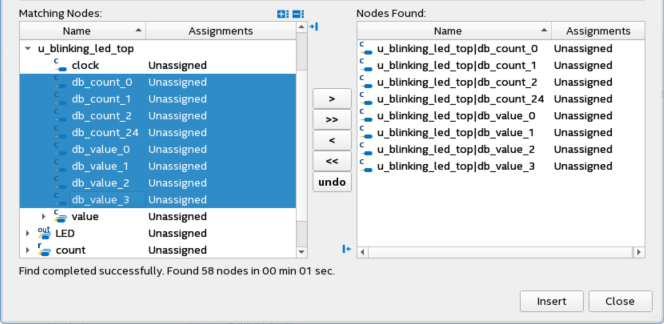

The Matching Nodes list shows signals that match the search criteria. - Add the boundary ports from the imported partition (db_*) from u_blinking_led_top to the Nodes Found list.

The names must match what appears in the Developer project's report file.

Figure 28. Node Finder Note: If you add nodes other than the db_* nodes from the imported partition, the Compiler leaves them unconnected.

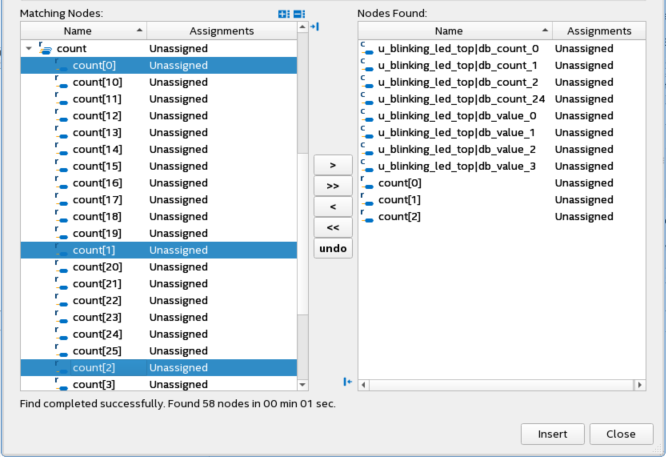

Note: If you add nodes other than the db_* nodes from the imported partition, the Compiler leaves them unconnected. - Add nodes count[2:0] from the root partition to the Nodes Found list, and click Insert.

Figure 29. Node Finder Copy Nodes

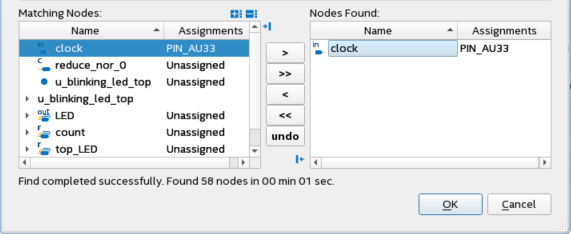

- Configure the Signal Tap acquisition. Refer to Step 6: Creating a Signal Tap File (Optional) for details.

Figure 30. Specifying the Clock Source

- Click File > Save, and save the file as stp_core_partition_reuse.stp.

A dialog box appears asking if you want to enable Signal Tap file for the project.

- Click Yes, and close the file.

Related Information