AN 847: Signal Tap Tutorial with Design Block Reuse: for Intel® Arria® 10 FPGA Development Board

ID

683712

Date

12/21/2020

Public

1. Introduction

2. Core Partition Reuse Debug—Developer

3. Core Partition Reuse Debug—Consumer

4. Root Partition Reuse Debug—Developer

5. Root Partition Reuse Debug—Consumer

6. AN 847: Signal Tap Tutorial with Design Block Reuse for Intel® Arria® 10 FPGA Development Board Archives

7. Document Revision History for AN 847: Signal Tap Tutorial with Design Block Reuse for Intel® Arria® 10 FPGA Development Board

2.1. Step 1: Creating a Core Partition

2.2. Step 2: Creating Partition Boundary Ports

2.3. Step 3: Compiling and Checking Debug Nodes

2.4. Step 4: Exporting the Core Partition and Creating the Black Box File

2.5. Step 5: Copying Files to Consumer Project

2.6. Step 6: Creating a Signal Tap File (Optional)

2.7. Step 7: Programming the Device and Verifying the Hardware

2.8. Step 8: Verifying Hardware with Signal Tap

3.1. Step 1: Adding Files and Running Synthesis

3.2. Step 2: Creating a Signal Tap File

3.3. Step 3: Creating a Partition for blinking_led_top

3.4. Step 4: Compiling the Design and Verifying Debug Nodes

3.5. Step 5: Programming the Device and Verifying the Hardware

3.6. Step 6: Verifying Hardware with Signal Tap

4.1. Step 1: Creating a Reserved Core Partition and Defining a Logic Lock Region

4.2. Step 2: Generating and Instantiating SLD JTAG Bridge Agent in the Root Partition

4.3. Step 3: Generating and Instantiating the SLD JTAG Bridge Host

4.4. Step 4: Generating HDL Instance of Signal Tap

4.5. Step 5: Compiling Export Root Partition and Copying Files to Consumer Project

4.6. Step 6: Programming the Device and Verifying the Hardware

4.7. Step 7: Generating a Signal Tap File for the Root Partition

4.8. Step 8: Verifying the Hardware with Signal Tap

5.1. Step 1: Adding Files to Customer Project

5.2. Step 2: Generating and Instantiating SLD JTAG Bridge Host in Reserved Core Partition

5.3. Step 3: Synthesizing, Creating Signal Tap File, and Compiling

5.4. Step 4: Programming the Device and Verifying the Hardware

5.5. Step 5: Verifying the Hardware of Reserved Core Partition with Signal Tap

5.6. Step 6: Verifying Hardware of Root Partition with Signal Tap

5.5. Step 5: Verifying the Hardware of Reserved Core Partition with Signal Tap

To use Signal Tap GUI for the reserved core:

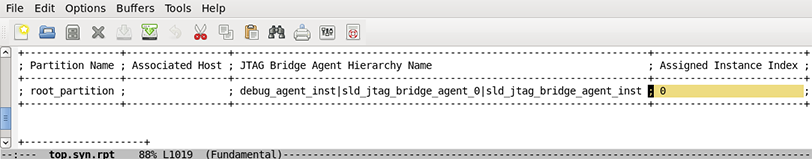

- Determine the bridge index according to the number in the synthesis report file (Root_Partition_Reuse/Developer/output_files/top.syn.rpt), under JTAG Bridge Agent Instance Information in the Developer project.

Figure 41. Synthesis Report

- In the Signal Tap window, click File > Open, and open stp_periphery_reuse_core.stp.

- Ensure that the development kit is powered ON and connected to the machine from which you open the Signal Tap logic analyzer.

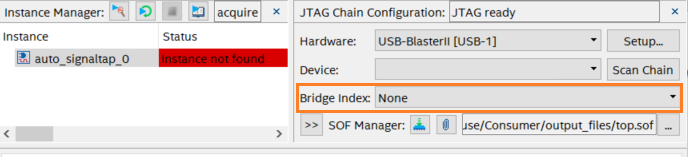

- Set up the JTAG Chain Configuration, and ensure Instance Manager is Ready to acquire.

- Set the Bridge Index as found in the synthesis report (Root_Partition_Reuse/Developer/output_files/top.syn.rpt in the Developer Project

If the values for Bridge Index are different, Signal Tap reports Instance not found.Figure 42. Setting the Bridge Index

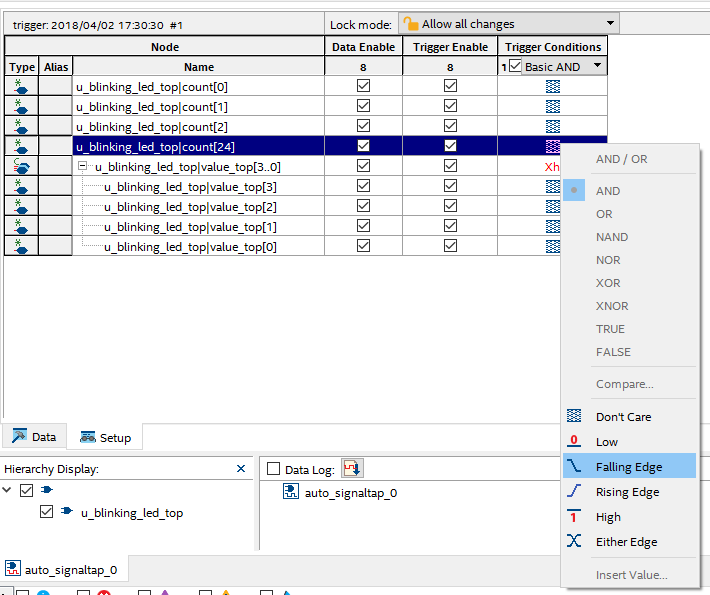

- To set the trigger condition, select count[24], right click the column under Trigger Conditions and select Falling Edge.

Figure 43. Trigger Conditions

- Run analysis by clicking Processing > Run Analysis.

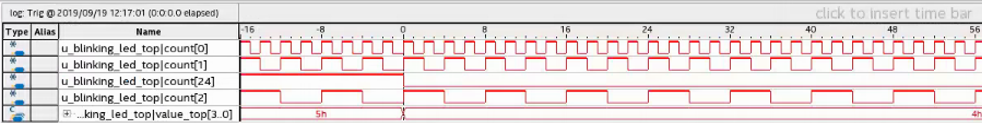

When the analysis finishes, the Waveform tab shows the captured data.

- Verify the transition of reserved core nodes in Signal Tap GUI. The expected behavior is:

- value_top[0] transitions along with count[24].

- count[0], count[1], and count[2] show the transition of other counter bits in the reserved core partition during this process.

Figure 44. Waveforms for reserved core Partition Nodes in Consumer Project

Related Information