F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide

ID

711009

Date

4/03/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP Core

2. Interface Overview

3. Parameters

4. Designing with the IP Core

5. Block Description

6. Configuration Registers

7. F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide Archives

8. Document Revision History for F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide

4.1. Generating Dynamic Reconfiguration Design and Configuration Profiles

4.2. Dynamic Reconfiguration QSF Settings

4.3. Dynamic Reconfiguration Using QSF-driven Flow

4.4. Dynamic Reconfiguration Rules

4.5. Hardware States and Configuration Profiles

4.6. Nios® -Based Dynamic Reconfiguration Flow

4.7. Using the Tile Assignment Editor

4.8. Visualizing Dynamic Reconfiguration Group Placement

4.9. Assigning IP_COLOCATE Hierarchy

4.10. Example: Dynamic Reconfiguration with Multirate IP Flow

4.11. Example: Dynamic Reconfiguration Programming Sequence

4.12. Dynamic Reconfiguration Error Recovery Handling

4.13. Determining Profile Numbers

4.14. Master Clock Channel

4.15. Using the IP_RECONFIG_GROUP_PARENT QSF Assignment

6.1. Dynamic Reconfiguration New Trigger

6.2. Dynamic Reconfiguration Next Profile 0

6.3. Dynamic Reconfiguration Next Profile 1

6.4. Dynamic Reconfiguration Next Profile 2

6.5. Dynamic Reconfiguration Next Profile 3

6.6. Dynamic Reconfiguration Next Profile 4

6.7. Dynamic Reconfiguration Next Profile 5

6.8. Dynamic Reconfiguration Next Profile 6

6.9. Dynamic Reconfiguration Next Profile 7

6.10. Dynamic Reconfiguration Next Profile 8

6.11. Dynamic Reconfiguration Next Profile 9

6.12. Dynamic Reconfiguration Next Profile 10

6.13. Dynamic Reconfiguration Next Profile 11

6.14. Dynamic Reconfiguration Next Profile 12

6.15. Dynamic Reconfiguration Next Profile 13

6.16. Dynamic Reconfiguration Next Profile 14

6.17. Dynamic Reconfiguration Next Profile 15

6.18. Dynamic Reconfiguration Next Profile 16

6.19. Dynamic Reconfiguration Next Profile 17

6.20. Dynamic Reconfiguration Next Profile 18

6.21. Dynamic Reconfiguration Next Profile 19

6.22. Dynamic Reconfiguration Avalon MM Timeout

6.23. Dynamic Reconfiguration TX Channel Reconfiguration

6.24. Dynamic Reconfiguration RX Channel Reconfiguration

6.25. Dynamic Reconfiguration TX Channel in Reset Acknowledgment

6.26. Dynamic Reconfiguration TX Channel out of Reset

6.27. Dynamic Reconfiguration TX Channel Reset Control Init Status

6.28. Dynamic Reconfiguration TX Channel Source Alarm

6.29. Dynamic Reconfiguration RX Channel in Reset Acknowledgment

6.30. Dynamic Reconfiguration RX Channel out of Reset

6.31. Dynamic Reconfiguration RX Channel Reset Control Init Status

6.32. Dynamic Reconfiguration RX Channel Source Alarm

6.33. Dynamic Reconfiguration Local Error Status

3. Parameters

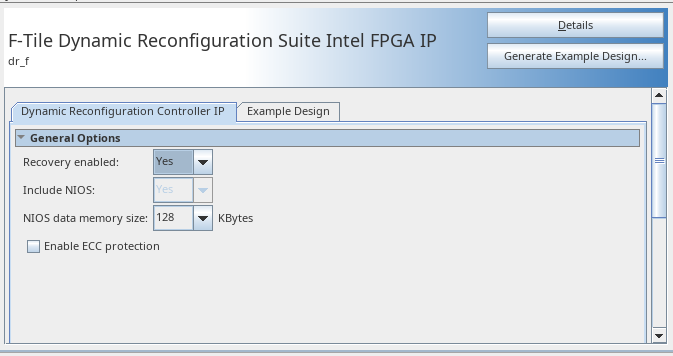

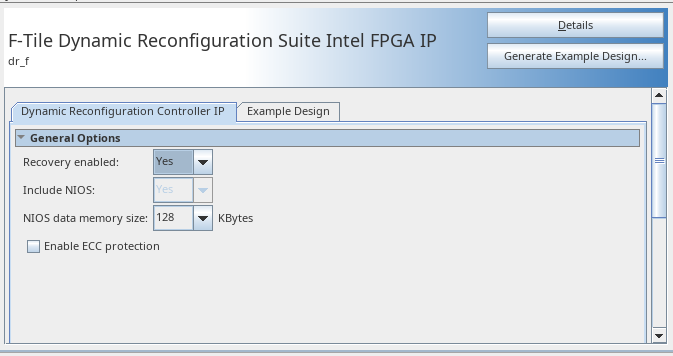

You customize the IP core by specifying parameters in the IP parameter editor.

Figure 1. F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP

| Parameter |

Range |

Default Setting |

Parameter Description |

|---|---|---|---|

| General Options | |||

| Recovery enabled |

|

Yes |

|

| Include NIOS |

|

Yes | Dynamic reconfiguration facilitated by NIOS inside the DR controller soft IP. |

| NIOS data memory size |

|

128 | NIOS on-chip data memory used to store memory initialization file (.mif) for dynamic reconfiguration. |

| Enable ECC protection |

|

Off | Enable ECC protection |