External Memory Interfaces Agilex™ 7 F-Series and I-Series FPGA IP User Guide

11.8. Using the Default Traffic Generator

The Traffic Generator also compares the written data and the read data, and sets one of the following status bits:

- traffic_gen_pass (TGP ISSP): Indicates that all write and read commands were sent to the EMIF, all read responses were received, and all writes and reads matched as expected.

- traffic_gen_fail (TGF ISSP): Indicates that all write and read commands were sent to the EMIF, all read responses were received, but one or more write-read mismatches have occurred.

- traffic_gen_timeout (TGT ISSP): Indicates that one or more of the expected read responses were not received.

For general information about the generated EMIF design example, refer to the External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP Design Example User Guide.

Each operation generated by the traffic generator is a single write or block of writes followed by a single read or block of reads to the same addresses, which allows the driver to precisely determine the data that should be expected when the memory interface returns the read data.

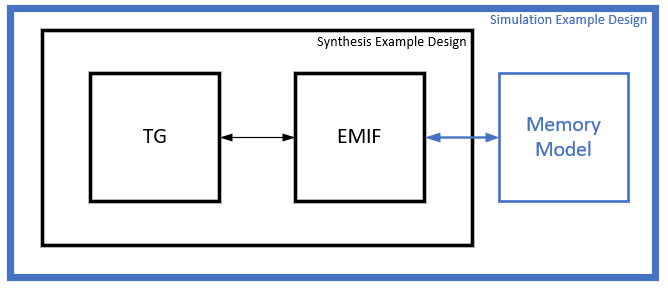

The traffic generator comprises a traffic generation block, the Avalon® memory-mapped interface and a read comparison block. The traffic generation block generates addresses and write data, which are then sent out over the Avalon® memory-mapped interface. The read comparison block compares the read data received from the Avalon® memory-mapped interface to the write data from the traffic generator. If at any time the data received is not the expected data, the read comparison block records the failure, finishes reading all the data, and then signals that there is a failure and the traffic generator enters a fail state. If all patterns are generated and compared successfully, the traffic generator enters a pass state.

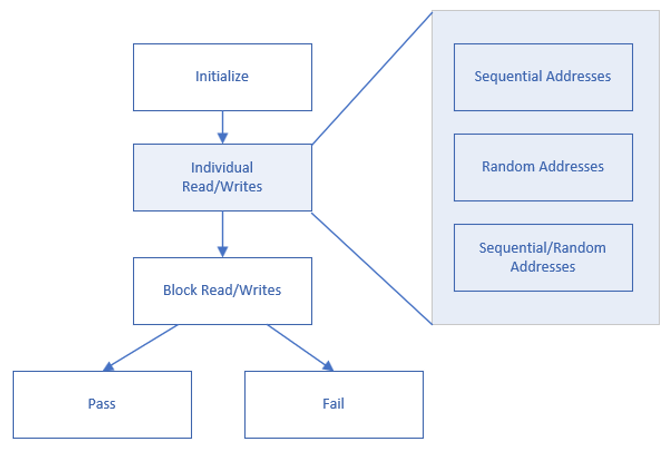

Within the traffic generator, there are the following main states:

- Generation of individual read and writes.

- Generation of block read and writes.

- The pass state.

- The fail state.

Within each of the generation states, there are the following substates:

- Sequential address generation.

- Random address generation.

- Mixed sequential and random address generation.

Read and Write Generation

The traffic generator can generate individual or block reads and writes. Individual read and write generation during the traffic generator’s individual read and write generation state, the traffic generation block generates individual write followed by individual read Avalon® memory-mapped interface transactions, where the address for the transactions is chosen according to the specific substate

Block read and Write Generation

During the traffic generator’s block read and write generation state, the traffic generator block generates a parameterizable number of write operations followed by the same number of read operations. The specific addresses generated for the blocks are chosen by the specific substates.

You can use the traffic generator for a variety of analysis and debugging applications, including the following:

- Verifying that an external memory interface is configured and working correctly, in simulation and in hardware.

- Evaluating the stability of the interface, as well as the calibration results. (Refer to the Driver Margining Tab topic.

- Isolating hardware issues such as single pin failures.

- Distinguishing between read failures and write failures.

- Running infinite traffic for hardware debugging.

- Measuring the efficiency of the interface.