Intel® Quartus® Prime Pro Edition User Guide: Debug Tools

A newer version of this document is available. Customers should click here to go to the newest version.

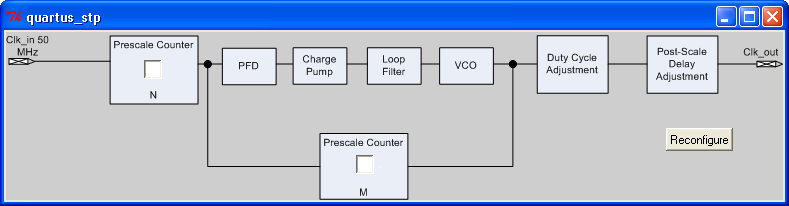

7.6. Design Example: Dynamic PLL Reconfiguration

Stratix® PLLs allow you to dynamically update PLL coefficients during run time. Each enhanced PLL within the Stratix® device contains a register chain that allows you to modify the pre-scale counters (m and n values), output divide counters, and delay counters. In addition, the ALTPLL_RECONFIG IP core provides an easy interface to access the register chain counters. The ALTPLL_RECONFIG IP core provides a cache that contains all modifiable PLL parameters. After you update all the PLL parameters in the cache, the ALTPLL_RECONFIG IP core drives the PLL register chain to update the PLL with the updated parameters. The figure shows a Stratix® -enhanced PLL with reconfigurable coefficients.

This design example was created using a Nios® II Development Kit, Stratix® Edition. The file sourceprobe_DE_dynamic_pll.zip contains all the necessary files for running this design example, including the following:

- Readme.txt—A text file that describes the files contained in the design example and provides instructions about running the Tk GUI shown in the figure below.

- Interactive_Reconfig.qar—The archived Intel® Quartus® Prime project for this design example.

Figure 110. Interactive PLL Reconfiguration GUI Created with Tk and In-System Sources and Probes Tcl Package