AN 957: Time-Sensitive Networking for Drive-on-Chip Design Example

ID

683707

Date

10/30/2021

Public

1. About the Time-Sensitive Networking for Drive-on-Chip Design Example

2. Getting Started with the TSN for Drive-on-Chip Design Example

3. Porting the Intel MAX 10 Drive-On-Chip design to the Cyclone V SoC Development Board

4. Running HPS Software for the TSN Drive-on-Chip Design

5. Connecting the Cyclone V SoC Development board to the Tandem 48 V Motion-Power board

6. Running the Program

7. TSN Configuration Example

8. Document Revision History for AN 957: Time-Sensitive Networking for Drive-on-Chip Design Example

A. Example .qsf for Pin Assignments and Attributes

B. Top-level Verilog HDL File Example

C. YOCTO Build Patch File (cvsx_doc_tsn_2_3-rt) for the TSN Drive-on-Chip Design Example

D. Script to read and change MAC addresses from Cyclone V SoC EEPROM

2.1. Hardware Requirements for the TSN for Drive-on-Chip Design Example

2.2. Software Requirements for the TSN for Drive-on-Chip Design Example

2.3. Configuring the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.4. Programming the FPGA for the TSN for Drive-on-Chip Design Example

2.5. Creating an SD Card Image for the TSN for Drive-on-Chip Design Example

2.6. Turning on the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.7. Configuring the TSN IP

3.1. Changing File Names, Revision Name, and Target Device for the TSN Drive-on-Chip Design Example

3.2. Modifying the Drive-On-Chip Qsys System

3.3. Adding the TTTech TSN IP to the Qsys system

3.4. Connecting the TSN and Drive-on-Chip Subsystems

3.5. Compiling the Quartus Prime Design and Top-Level Module

3.6. Generating the Preloader

3.7. Generating a .jic file

3.8. Compiling the Drive-on-Chip Design Software in Nios II Software Build Tools

3.9. Launching a YOCTO Build

3.10. Building an SD Card Image for the TSN Drive-on-Chip Design Example

3.11. Changing MAC Addresses

3.12. Reading and Checking Physical Addresses on the Cyclone V SoC Development Board

3.1. Changing File Names, Revision Name, and Target Device for the TSN Drive-on-Chip Design Example

- Change the name to differentiate the new project. For example, for the .qpf file DOC_TANDEM_CVSX_NIOS_TSN, as this variation of the project includes the drive-on-chip based on Nios II soft-processor and the TSN IP.

You can also change the name of the .qsys file.

- In Intel Quartus Prime 17.0, navigate to File > Open Project and select the newly-named .qpf file.

- Apply the following changes;

- Create a new revision of the project, by selecting Project > Revisions and add a new revision based on DOC_TANDEM_MAX_10, for example DOC_TANDEM_CVSX_NIOS_TSN.

- Remove the previous revision.

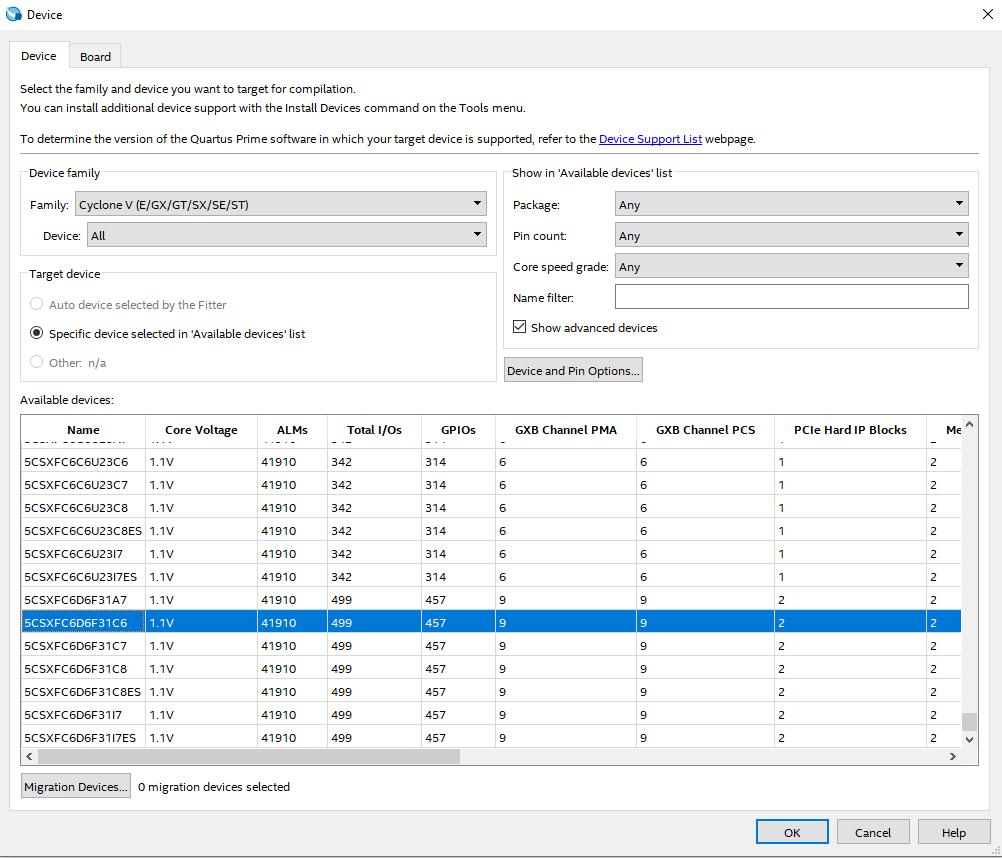

- Change the target device, by selecting Assignments > Device > 5CSXFC6D6F31C6:

Figure 5. Selected Device

- Change the name of the top-level Verilog HDL file from to DOC_TANDEM_MAX10.v to DOC_TANDEM_CVSX_NIOS_TSN.v

- In the new top-level Verilog HDL file, change the name of the main Qsys instance u-doc to match the name of the .qsys file. For example: DOC_TANDEM_CVSX_NIOS_TSN_QSYS