3.3.5. Serial Protocol Interface (SPI)

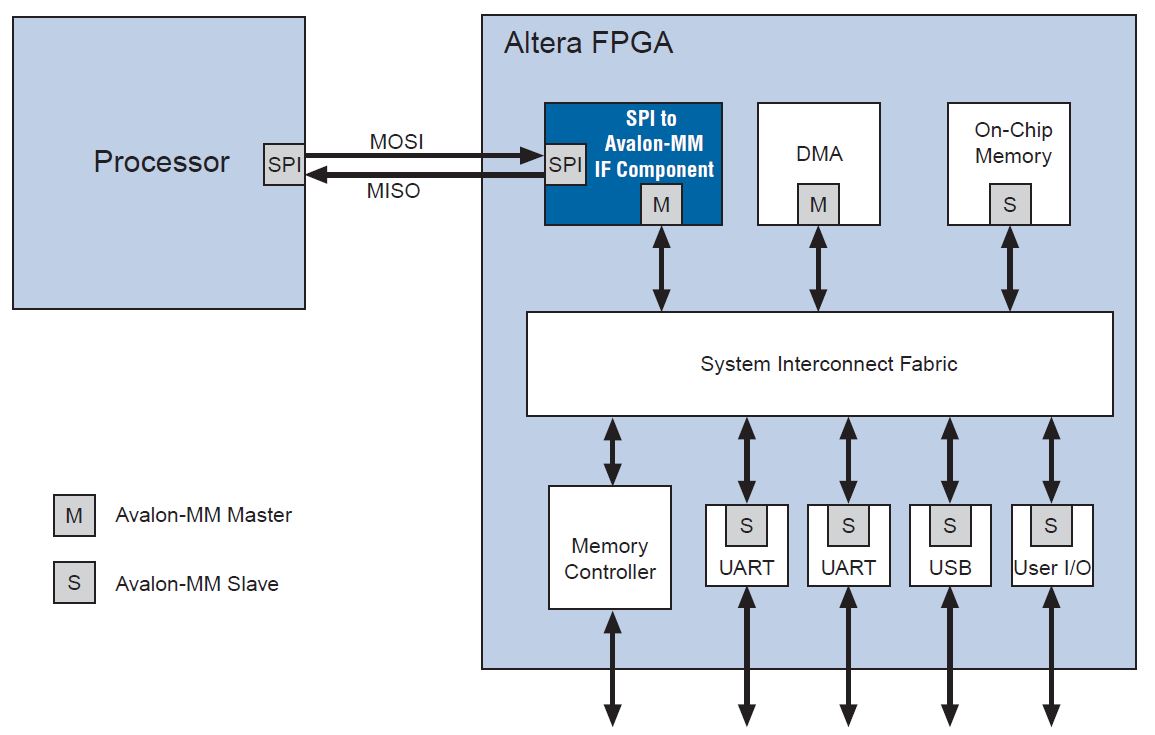

The SPI Slave to Avalon® Master Bridge component provides a simple connection between processors and Platform Designer systems through a four-wire industry standard serial interface. Host systems can initiate Avalon® -MM transactions by sending encoded streams of bytes through the core's serial interface. The core supports read and write transactions to the Platform Designer system for memory access and peripheral expansion.

The SPI Slave to Avalon® Master Bridge is an Platform Designer-ready component that integrates easily into any Platform Designer system. Processors that include an SPI interface can easily encapsulate Avalon® -MM transactions for reads and writes using the protocols outlined in the SPI Slave/JTAG to Avalon® Master Bridge Cores chapter of the Embedded Peripherals IP User Guide.

Details of each protocol layer can be found in the following chapters of the Embedded Peripherals IP User Guide:

SPI Slave/JTAG to Avalon® Master Bridge Cores—Provide a connection from an external host system to an Platform Designer system. Allow an SPI master to initiate Avalon® -MM transactions.

Avalon® -ST Bytes to Packets and Packets to Bytes Converter Cores—Provide a connection from an external host system to an Platform Designer system. Allow an SPI master to initiate Avalon® -ST transactions.

Avalon® Packets to Transactions Converter Core—Receives streaming data from upstream components and initiates Avalon® -MM transactions. Returns Avalon® -MM transaction responses to requesting components.

The SPI Slave to Avalon® Master Bridge Design Example demonstrates SPI transactions between an Avalon® -MM host system and a remote SPI system.