3.4.3. Nios® II Processor Data Accesses

In the Nios® II processor, the internal arithmetic byte ordering and the bus byte ordering are both little endian. Internally, the processor and its compiler map the least significant byte of a value to the lowest byte offset in memory.

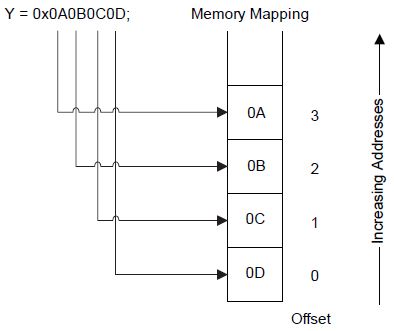

For example, the figure below shows storing the 32-bit value 0x0A0B0C0D to the variable Y. The action maps the least significant byte 0x0D to offset 0 of the memory used to store the variable.

The Nios® II processor is a 32-bit processor. For data larger than 32 bits, the same mapping of the least significant byte to lowest offset occurs. For example, if the value 0x0807060504030201 is stored to a 64-bit variable, the least significant byte 0x01 of the variable is stored to byte offset 0 of the variable in memory. The most significant byte 0x08 of the variable is stored to byte offset 7 of the variable in memory. The processor writes the least significant four bytes 0x04030201 of the variable to memory first, followed by the most significant four bytes 0x08070605.

The master interfaces of the Nios® II processor comply with Avalon® -MM bus byte ordering by providing read and write data to the interconnect in descending bit order with bits 7 down to 0 representing byte offset 0. Because the Nios® II processor uses a 32-bit data path, the processor can access the interconnect with seven different aligned accesses. The table below shows the seven valid write accesses that the Nios® II processor can present to the interconnect.

| Access Size (Bits) | Offset (Bytes) | Value | Byte Enable (Bits 3:0) | Write Data (Bits 31:24) | Write Data (Bits 23:16) | Write Data (Bits 15:8) | Write Data (Bits 7:0) |

|---|---|---|---|---|---|---|---|

| 8 | 0 | 0x0A | 0001 | — | — | — | 0x0A |

| 8 | 1 | 0x0A | 0010 | — | — | 0x0A | — |

| 8 | 2 | 0x0A | 0100 | — | 0x0A | — | — |

| 8 | 3 | 0x0A | 1000 | 0x0A | — | — | — |

| 16 | 0 | 0x0A0B | 0011 | — | — | 0x0A | 0x0B |

| 16 | 2 | 0x0A0B | 1100 | 0x0A | 0x0B | — | — |

| 32 | 0 | 0x0A0B0C0D | 1111 | 0x0A | 0x0B | 0x0C | 0x0D |

The code fragment shown in the example generates all seven of the accesses described in the table in the order presented in the table, where BASE is a location in memory aligned to a four-byte boundary.

Nios® II Write Data Byte Mapping Code

IOWR_8DIRECT(BASE, 0, 0x0A); IOWR_8DIRECT(BASE, 1, 0x0A); IOWR_8DIRECT(BASE, 2, 0x0A); IOWR_8DIRECT(BASE, 3, 0x0A); IOWR_16DIRECT(BASE, 0, 0x0A0B); IOWR_16DIRECT(BASE, 2, 0x0A0B); IOWR_32DIRECT(BASE, 0, 0x0A0B0C0D);