Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

6/09/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Host Operating System Check for Ubuntu v22.04

3.5.6. Installing the Required Kernel Version for Ubuntu v24.04

3.5.7. Set the Boot Parameters

3.5.8. MCDMA Custom Driver

3.5.9. MCDMA DPDK Poll Mode Driver

3.5.10. MCDMA Kernel Mode Network Device Driver

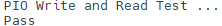

3.5.8.2. PIO Test

This test writes and reads from the PIO memory and validates the data. If data validation passes, the result is a Pass; otherwise, it is a Fail.

- Perform a PIO test after completing the instructions outlined in Prerequisites to check if the setup works correctly by running the command below:

$sudo ./perfq_app -b 0000:08:00.0 -o

Note: Here the -b option should be provided with the correct BDF of the FPGA endpoint card in the system. It can be checked using the lspci command.If successful, the application displays a Pass status as shown in the image below:

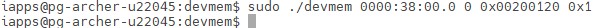

- The design example can be reset using the utility below when needed.

- Build the devmem utility.

Note: The devmem utility works only with the ifc_uio driver.

$ cd software/user/cli/devmem

$ make clean all

- Perform a reset by running the command below:

$ sudo ./devmem 0000:01:00.0 0 0x00200120 0x1

Expected printout looks like the image below:

- Build the devmem utility.