Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

6/09/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Host Operating System Check for Ubuntu v22.04

3.5.6. Installing the Required Kernel Version for Ubuntu v24.04

3.5.7. Set the Boot Parameters

3.5.8. MCDMA Custom Driver

3.5.9. MCDMA DPDK Poll Mode Driver

3.5.10. MCDMA Kernel Mode Network Device Driver

3.5.8.3.3.1. DMA Test Beyond 256 Channels

For a design example generated with the number of channels > 256, follow this procedure.

- Enable the following software flags in p0_software/user/common/mk/common.mk:

__cflags += -DIFC_MCDMA_DIDF

__cflags += -UIFC_MCDMA_SINGLE_FUNC

- Configure the static channel mapping in p0_software/user/cli/perfq_app/perfq_app.h as mentioned in the previous DMA test command for the Packet Generate/Check design example.

- If the Linux kernel driver has been installed, build the driver and application by following the instructions in Build and Install the User Space Library and Build the Reference Application. Otherwise, the Linux kernel driver needs to be installed before building the driver and application.

Command:

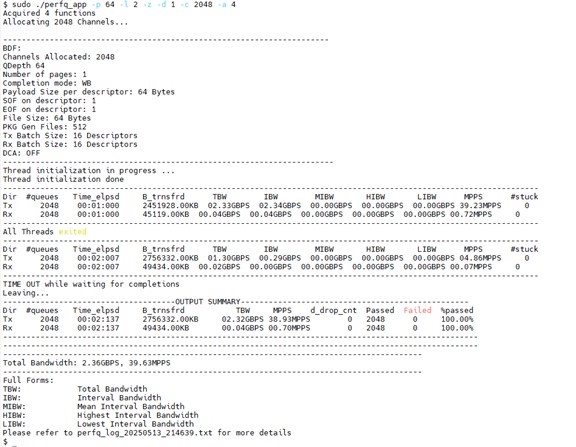

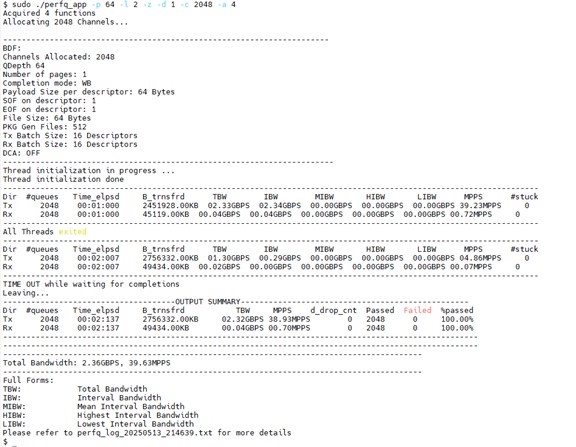

sudo ./perfq_app -p 64 -l 2 -z -d 1 -c 2048 -a 4

Configuration:- 2K channels (-c 2048)

- Packet Generate bidirectional (-z)

- Payload length of 64 bytes (-p 64)

- Transfer the data in 2 seconds (-l 2)

- Number of threads that needs to be used (-a 4)

- Dump the progress logs every second (-d 1)

Figure 35. Packet Generate/Check DMA Hardware Test Result with 2048 Channels

Note:

- For a test with 2048 channels, the following configurations can be used:

With SR-IOV: 2 PFs (512 channels per PF) and 2 VFs per PF (256 channels per VF)

Without SR-IOV: 4 PFs (512 channels per PF)

- Currently, in DIDF mode, a single page is supported.

- Simultaneous process currently cannot be supported in DIDF mode. You can run one process with 2k channels.