Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

6/09/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Host Operating System Check for Ubuntu v22.04

3.5.6. Installing the Required Kernel Version for Ubuntu v24.04

3.5.7. Set the Boot Parameters

3.5.8. MCDMA Custom Driver

3.5.9. MCDMA DPDK Poll Mode Driver

3.5.10. MCDMA Kernel Mode Network Device Driver

3.5.9.4. BAM Test

- If the BAM is enabled in the design example, set the following flags in: p0_software/dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h:

#define IFC_PIO_256 ➤ 256b read/write operations on PIO BAR and undef other size or #define IFC_PIO_128 ➤ 128b read/write operations on PIO BAR and undef other size

- To enable 256-bit read or write operations, set the software flags as shown below in: p0_software/dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h

#define IFC_PIO_256 #undef IFC_PIO_128

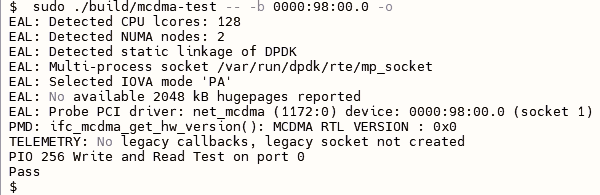

Figure 47. Test Results for 256-bit DPDK

- To enable 128-bit read or write operations, set the software flags as shown below in p0_software/dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h

#undef IFC_PIO_256 #define IFC_PIO_128

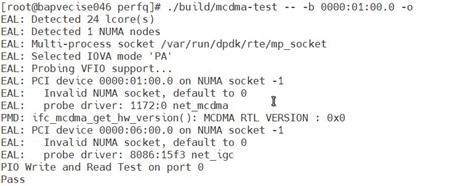

Figure 48. PIO 128b Write and Read Test

- To enable 256-bit read or write operations, set the software flags as shown below in: p0_software/dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h

- For PIO using Bypass with BAM/BAS user mode, you must undefine the following software flag:

#undef IFC_QDMA_INTF_ST (p0_software/user/common/include/mcdma_ip_params.h)

- Follow the instructions outlined in Prerequisites to build and install the driver.

- Run the test using the following commands:

$ cd dpdk-stable/build/examples/mcdma-test/perfq

$ sudo ./build/mcdma-test -- -b 0000:01:00.0 -o