Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

6/09/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Host Operating System Check for Ubuntu v22.04

3.5.6. Installing the Required Kernel Version for Ubuntu v24.04

3.5.7. Set the Boot Parameters

3.5.8. MCDMA Custom Driver

3.5.9. MCDMA DPDK Poll Mode Driver

3.5.10. MCDMA Kernel Mode Network Device Driver

2.5.2. Hardware Test Results

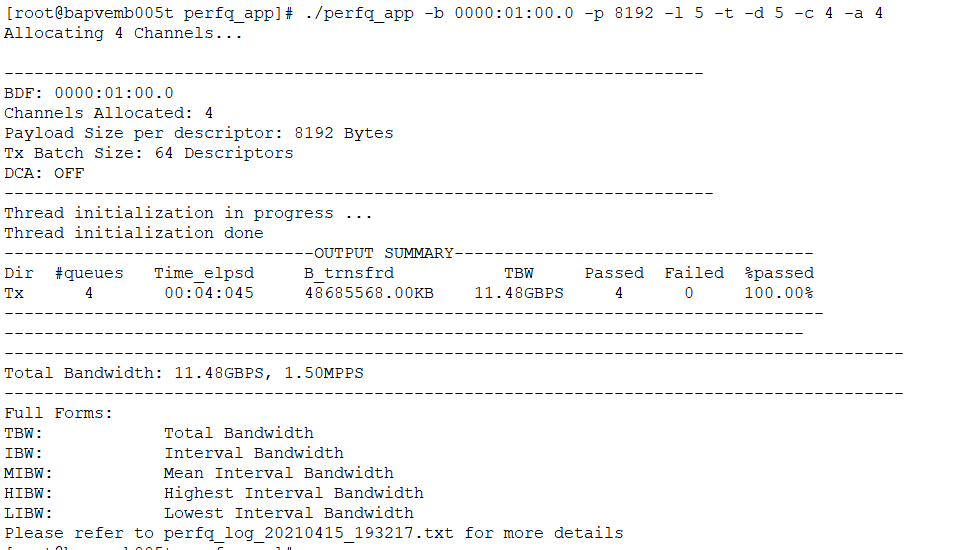

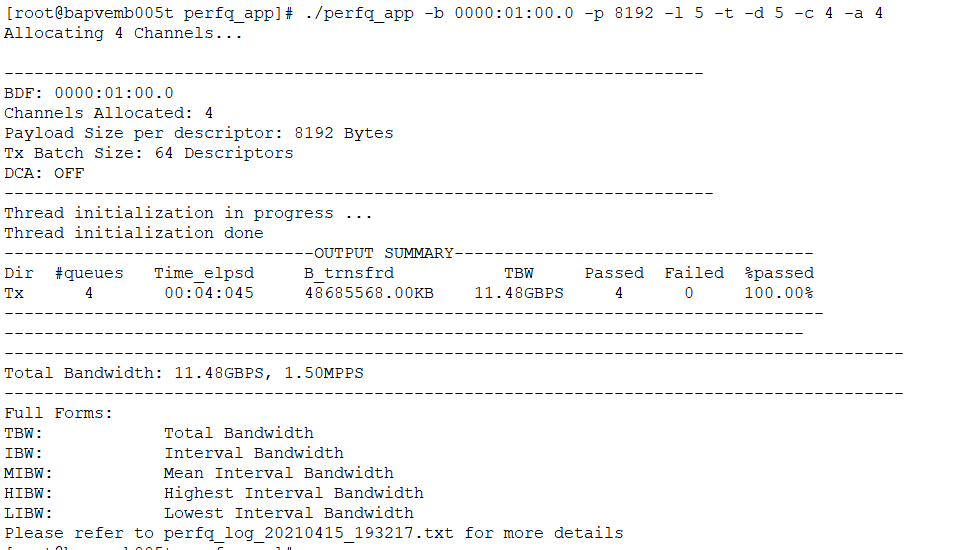

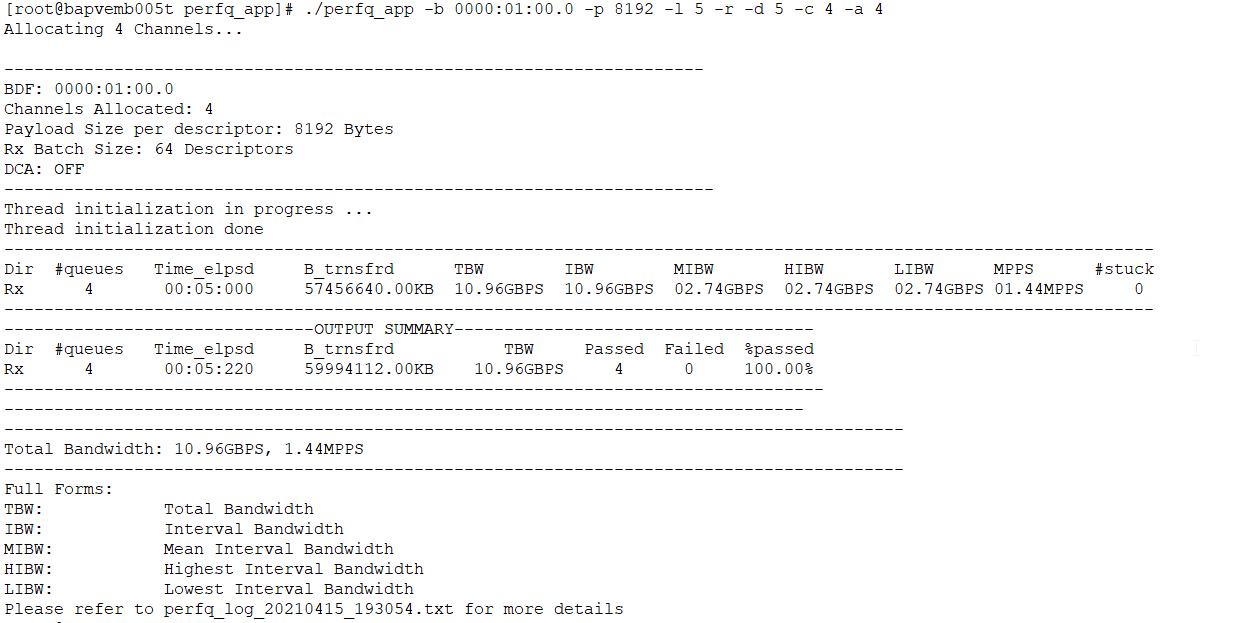

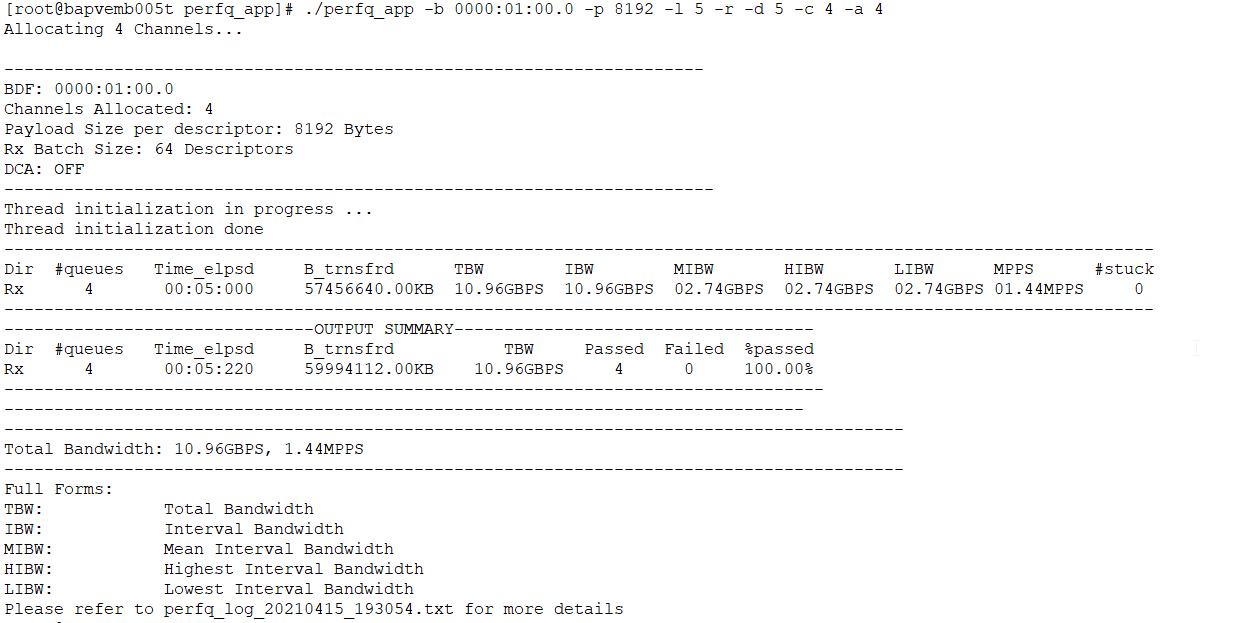

The Custom Driver was used to generate the following output:

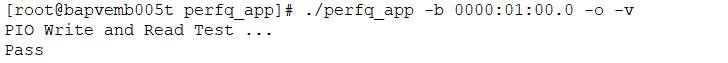

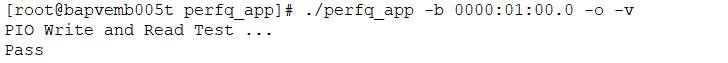

Figure 15. PIO Test-o option

Figure 16. H2D Avalon-MM Write-t option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

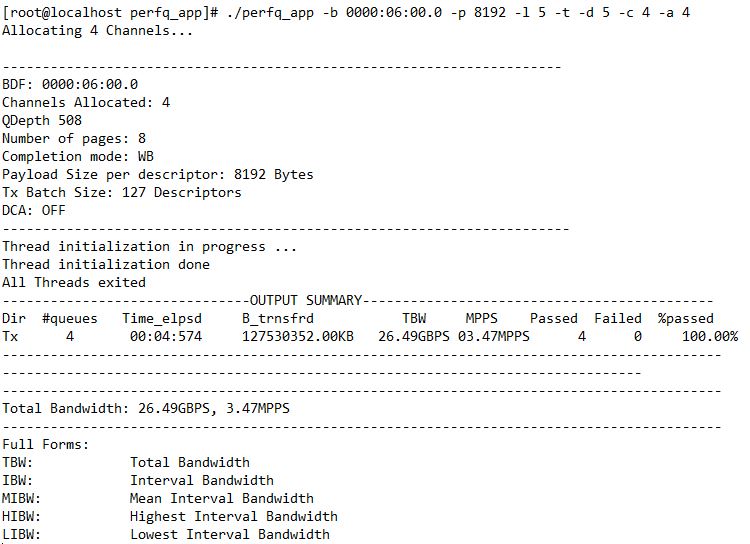

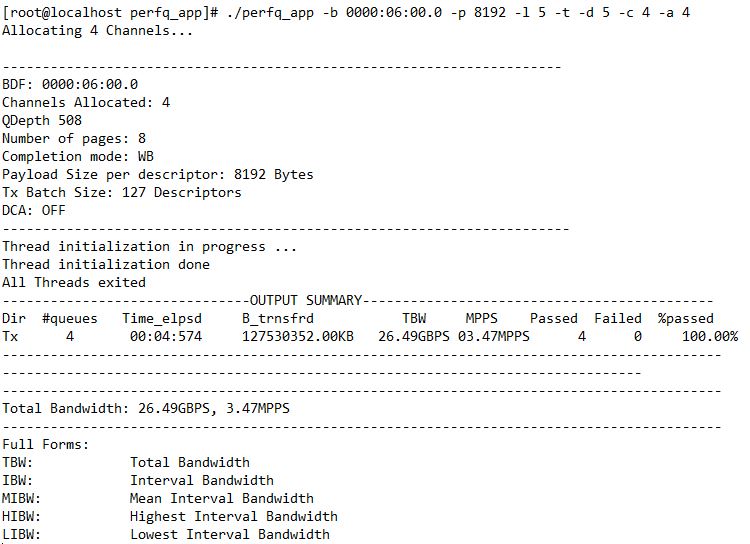

Figure 17. H2D Avalon-MM Write Agilex™ 7 F-Series P-Tile PCIe Gen4 x16 The following hardware test was run with Agilex™ 7 F-Series P-Tile PCIe Gen4 x16 configuration using Custom Driver.

Figure 18. H2D Avalon-MM Write with Data Validation Enabled-t -v option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

To enable data validation using -v option, set the software flags in user/common/mk/common.mk as follows:

cflags += -UPERFQ_PERF cflags += -DPERFQ_LOAD_DATA

Note: Hardware test with P-Tile Gen4 x16 may be added in a future release.

Figure 19. D2H Avalon-MM Read-r option. Note: This hardware test was run with the Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

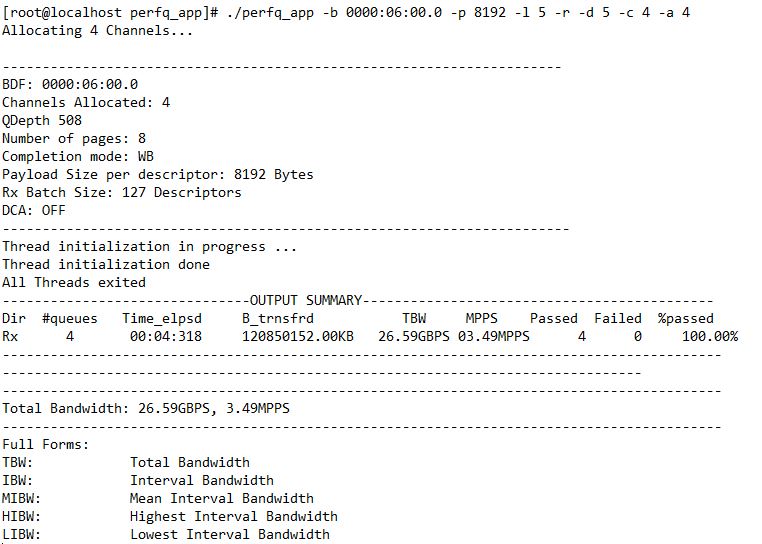

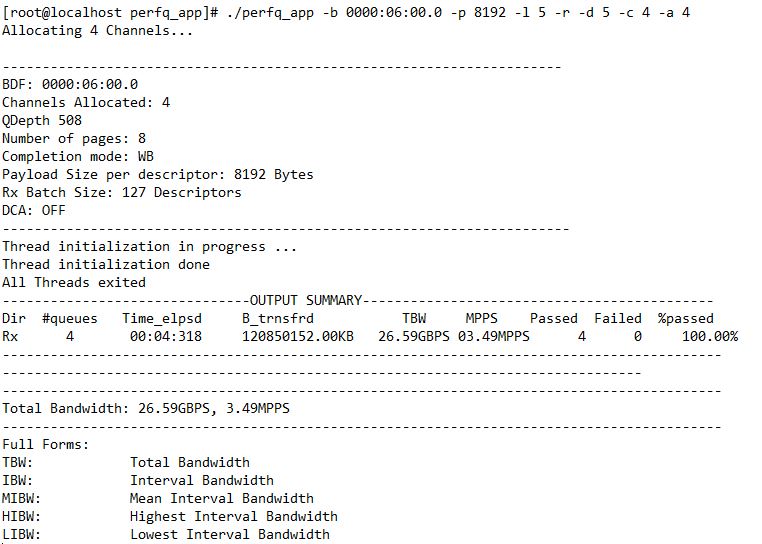

Figure 20. D2H Avalon-MM Read Agilex™ 7 F-Series P-Tile PCIe Gen4 x16