Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

6/09/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Host Operating System Check for Ubuntu v22.04

3.5.6. Installing the Required Kernel Version for Ubuntu v24.04

3.5.7. Set the Boot Parameters

3.5.8. MCDMA Custom Driver

3.5.9. MCDMA DPDK Poll Mode Driver

3.5.10. MCDMA Kernel Mode Network Device Driver

3.5.9.5. BAS Test

For x4 BAS:

- Set the PCIe_SLOT “2” in rte_pmd_mcdma.h (p0_software/dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h).

- X4 BAS supports a burst length of 32 by default. In the file perfq_app.h (p0_software/dpdk/dpdk/examples/mcdma-test/perfq/perfq_app.h)

#define IFC_MCDMA_BAS_X4_BURST_LENGTH 32

For the Traffic Generator/Checker design example, you must disable the MSI-X parameter, IFC_QDMA_MSIX_ENABLE, in the file "p0_software/dpdk/dpdk/drivers/net/mcdma/base/mcdma_ip_params.h" if MSI-X is not enabled in the IP Parameter Editor GUI. By default, the DPDK Driver software parameter is enabled and MSI-X is disabled in the IP. This mismatch prevents the ifc_uio kernel module from being loaded.

Note: Refer to Design Example BAR Mappings for BAR mapping information.

Commands:

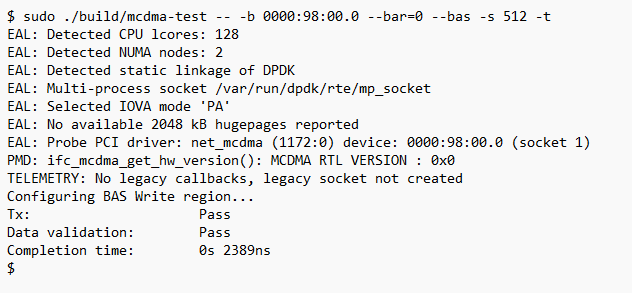

- To verify the write operation:

$ sudo ./build/mcdma-test -- -b 0000:01:00.0 --bar=0 \ --bas -s 512 -t

Figure 49. BAS Write Operation

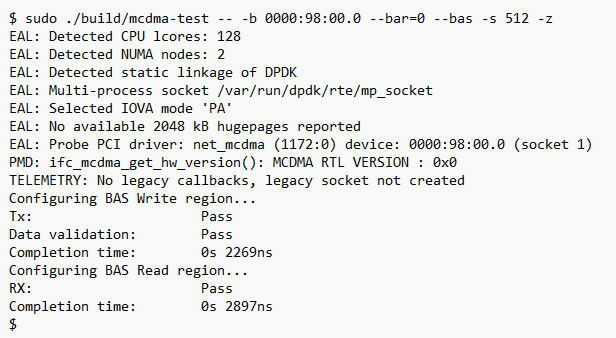

- To verify the read operation:

$ sudo ./build/mcdma-test -- -b 0000:01:00.0 --bar=0 \ --bas -s 512 -r

Figure 50. BAS Read Operation

- To verify the write and read operations:

$ sudo ./build/mcdma-test -- -b 0000:01:00.0 --bar=0 \ --bas -s 512 -z

Figure 51. BAS Write and Read Operations

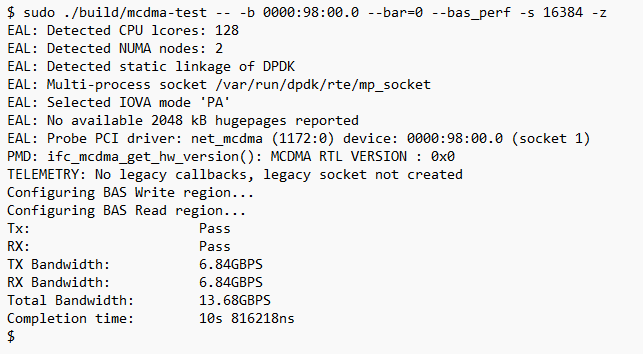

- Performance test:

The log below is collected on a Gen3 x16 H-Tile.

$ sudo ./build/mcdma-test -- -b 0000:01:00.0 --bar=0 \ --bas_perf -s 16384 -z

Figure 52. Performance Test

Note: For DPDK: VF/PF cannot run BAM+BAS+MCDMA simultaneously within one VM or hypervisor. You need to run one instance of VF/PF in an independent VM.