Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.9.3.3.1. DMA Test Beyond 256 Channels

If the design example is generated with the number of channels greater than 256, follow this procedure to run a DMA test.

- Define the following software flag in

p0_software/dpdk/dpdk/patches/v21.11.2/dpdk-stable/drivers/net/mcdma/rte_pmd_mcdma.h :

#define IFC_MCDMA_DIDF

- Configure the mem zone in

p0_software/dpdk/dpdk/patches/v21.11.2/dpdk-stable/config/rte_config.h .

#define RTE_MAX_MEMZONE 20480

- Undefine single function mode in

p0_software/dpdk/dpdk/patches/v21.11.2/dpdk-stable/examples/mcdma-test/perfq/meson.build .

-UIFC_MCDMA_SINGLE_FUNC

- Update the static channel mapping in

p0_software/dpdk/dpdk/patches/v21.11.2/dpdk-stable/examples/mcdma-test/perfq/perfq_app.h by modifying the following parameters:

/* PF count starts from 1 */

#define IFC_QDMA_CUR_PF <pf number>

/*VF count starts from 1. Zero implies PF was used instead of VF */

#define IFC_QDMA_CUR_VF <vf number>

/* Number of PFs */

#define IFC_QDMA_PFS <number of PFs>

/* Channels available per PF */

#define IFC_QDMA_PER_PF_CHNLS <number of channels per PF>

/* Channels available per VF */

#define IFC_QDMA_PER_VF_CHNLS <number of channels per VF>

/* Number of VFs per PF */

#define IFC_QDMA_PER_PF_VFS <number of VFs per PF>

- Rebuild the DPDK application using the following commands for the new settings to take effect.

$ cd p0_software/dpdk/dpdk/patches/v21.11.2/dpdk-stable/

$ sudo meson build --reconfigure

$ sudo DESTDIR=install ninja -C build install

$ cd build

$ sudo meson configure -Dexamples=mcdma-test/perfq -Denable_kmods=true

$ sudo ninja

- Navigate to the perfq folder:

$ cd examples/mcdma-test/perfq

- Verify the Packet Loopback design example variant using the following command:

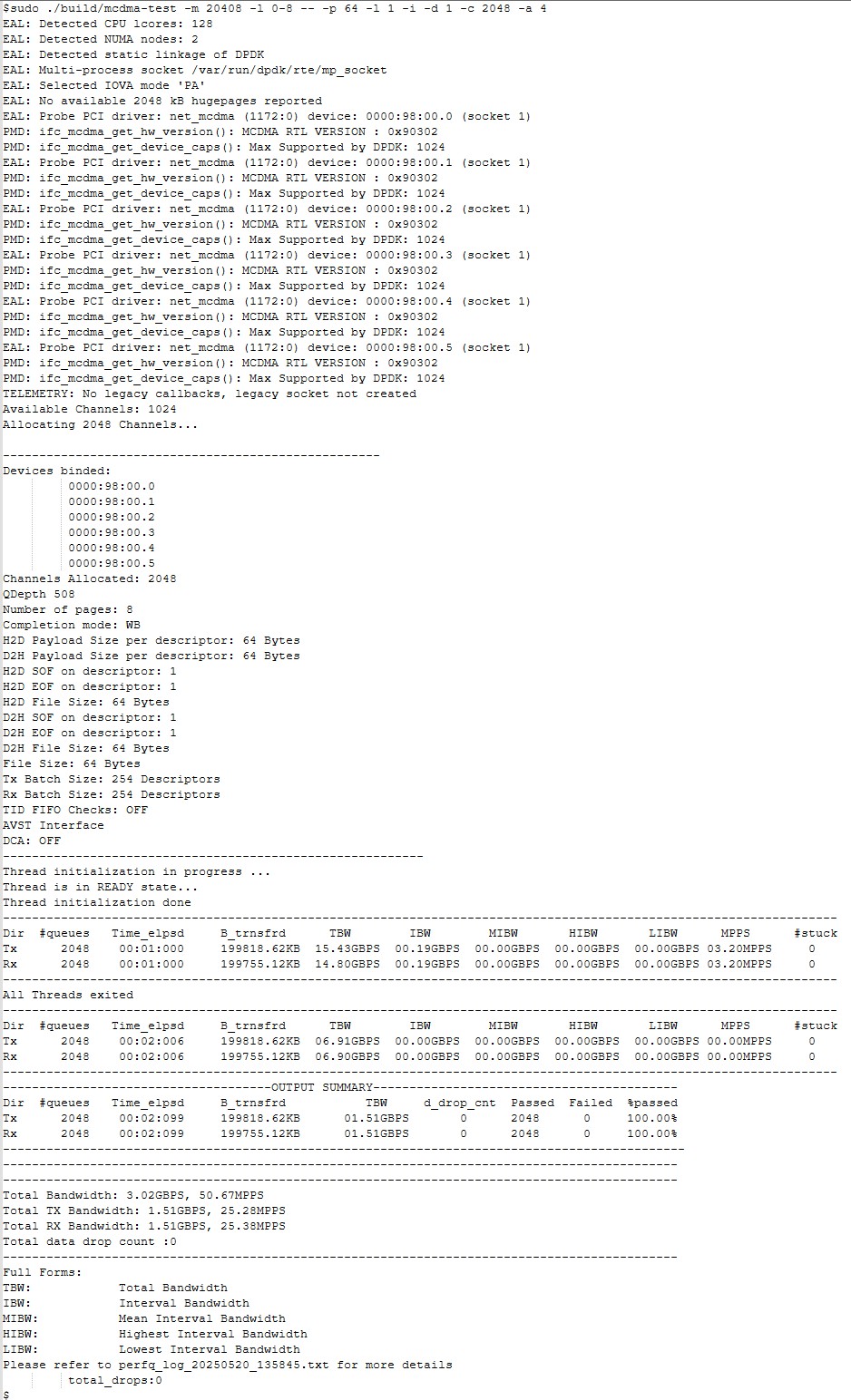

$ sudo ./build/mcdma-test -m 16384 -l 0-8 -- -p 64 -l 2 \ -i -d 1 -c 2048 -a 4

- With SR-IOV: 2 PFs (512 channels per PF) and 2 VFs per PF (256 channels per VF).

Without SR-IOV : 4 PFs (512 channels per PF).

- In the current release, a single page is supported in DIDF mode.

- In the current release, a simultaneous process is not supported in DIDF mode. You can run one process with 2K channels.