Intel® Quartus® Prime Standard Edition User Guide: Power Analysis and Optimization

ID

683506

Date

9/24/2018

Public

1.1. Comparison of the EPE and the Intel® Quartus® Prime Power Analyzer

1.2. Power Estimations and Design Requirements

1.3. Power Analyzer Walkthrough

1.4. Inputs for the Power Analyzer

1.5. Power Analysis in Modular Design Flows

1.6. Power Analyzer Compilation Report

1.7. Scripting Support

1.8. Power Analysis Revision History

1.4.2.1. Waveforms from Supported Simulators

1.4.2.2. .vcd Files from Third-Party Simulation Tools

1.4.2.3. Signal Activities from RTL (Functional) Simulation, Supplemented by Vectorless Estimation

1.4.2.4. Signal Activities from Vectorless Estimation and User-Supplied Input Pin Activities

1.4.2.5. Signal Activities from User Defaults Only

1.5.1. Complete Design Simulation

1.5.2. Modular Design Simulation

1.5.3. Multiple Simulations on the Same Entity

1.5.4. Overlapping Simulations

1.5.5. Partial Simulations

1.5.6. Node Name Matching Considerations

1.5.7. Glitch Filtering

1.5.8. Node and Entity Assignments

1.5.9. Default Toggle Rate Assignment

1.5.10. Vectorless Estimation

2.5.1. Clock Power Management

2.5.2. Pipelining and Retiming

2.5.3. Architectural Optimization

2.5.4. I/O Power Guidelines

2.5.5. Memory Optimization (M20K/MLAB)

2.5.6. DDR Memory Controller Settings

2.5.7. DSP Implementation

2.5.8. Reducing High-Speed Tile (HST) Usage

2.5.9. Unused Transceiver Channels

2.5.10. Periphery Power reduction XCVR Settings

1.3. Power Analyzer Walkthrough

The Intel® Quartus® Prime Power Analyzer requires post-fit design.

You must either provide timing assignments for all clocks in the design, or generate activity data from a simulation-based flow. You must specify the I/O standard on each device input and output, and the board trace model on each output in the design.

To run the Power Analyzer:

- From the Intel® Quartus® Prime Software, open the Power Analyzer tool by clicking Processing >

Power Analyzer Tool.

Power Analyzer Tool. - If you have signal activity information for the project, turn on Use input files to initialize toggle rates and static probabilities during power analysis, and then click Add Power Input Files to specify input files.

For more information about generating those input files, refer to Sources for Signal Activity Data.

- To direct the Power Analyzer to write a Signal Activity (.saf) output file, turn on Write out signal activities used during power analysis, and specify the file name.

- To direct the Power Analyzer to generate an Early Power Estimation file, turn on Write out Early Power Estimation file, and specify the file name.

With this file, you can import design information into the Early Power Estimator spreadsheet, and perform what-if analyses.

- Specify the default toggle rate for input I/O signals.

The Power Analyzer uses the default toggle rate when no other method specifies the signal-activity data.

- Specify the default toggle rate for the remaining (non input) signals.

- Define the cooling solution and temperature.

- Click Start.

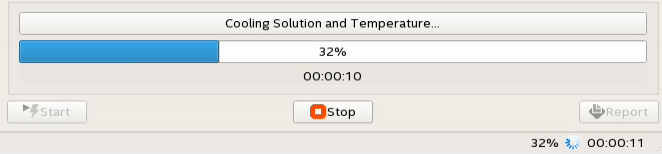

Figure 2. Progress Bar in Intel® Quartus® Prime Power Analyzer

- When the tool finishes, click Report to open the Power Analyzer report.

Related Information