A newer version of this document is available. Customers should click here to go to the newest version.

1. Overview

2. Quick Start Guide

3. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

4. Integrating the IP With Your Application

5. Simulating the IP

6. Validating the IP

A. Appendix A: Functional Description

B. Appendix B: Registers

C. Document Revision History for the GTS AXI Multichannel DMA IP for PCI Express*

2.1.1. Downloading and Installing Quartus® Prime Software

2.1.2. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

2.1.3. Configuring and Generating the GTS AXI Streaming Intel FPGA IP for PCI Express

2.1.4. Configuring and Generating the GTS System PLL Clocks Intel FPGA IP

2.1.5. Configuring and Generating the GTS Reset Sequencer Intel FPGA IP

2.1.6. Configuring and Generating the Reset Release IP

2.1.7. Instantiating and Connecting the IP Interfaces

2.1.8. Simulate, Compile and Validate the Design on Hardware

4.4.1. PCIe AXI-Stream TX Interface (ss_tx_st)

4.4.2. PCIe AXI-Stream RX Interface (ss_rx_st)

4.4.3. Control and Status Register Interface (ss_csr_lite)

4.4.4. Transmit Flow Control Credit Interface (ss_txcrdt)

4.4.5. Configuration Intercept Interface (CII)

4.4.6. Completion Timeout Interface (ss_cplto)

4.4.7. Function Level Reset (FLR) Interface

4.4.8. Control Shadow Interface (ss_ctrlshadow)

4.4.9. Error Interface

4.5.1. H2D AXI-Stream Manager (h2d_st_initatr)

4.5.2. D2H AXI-Stream Subordinate (d2h_st_respndr)

4.5.3. H2D/D2H AXI-MM Manager (dma_mm_initatr)

4.5.4. BAM AXI-MM Manager (bam_mm_initatr)

4.5.5. BAS AXI-MM Subordinate (bas_mm_respndr)

4.5.6. PIO AXI-Lite Manager (pio_lite_initiatr)

4.5.7. HIP Reconfiguration AXI-Lite Subordinate (user_csr_lite)

4.5.8. User Event MSI-X (user_msix)

4.5.9. User Event MSI (user_msi)

4.5.10. User Function Level Reset (user_flr)

4.5.11. User Configuration Intercept Interface

4.5.12. Configuration Slave (cs_lite_respndr)

A.1.1.1. H2D Data Mover

A.1.1.2. D2H Data Mover

A.1.1.3. Descriptors

A.1.1.4. AXI4-Lite PIO Manager

A.1.1.5. AXI-MM Write (H2D) and Read (D2H) Manager

A.1.1.6. AXI-Stream Manager (H2D) and Subordinate (D2H)

A.1.1.7. User MSI-X

A.1.1.8. User Function Level Reset (FLR)

A.1.1.9. Control and Status Registers

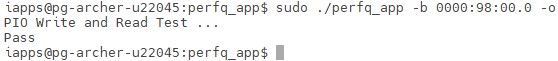

6.2.6.2. PIO Test

This test writes and reads from the PIO memory and validates the data. If data validation passes, then the result is Pass; else, it is Fail.

- Perform a PIO test after completing the instructions outlined in Prerequisites to check if the setup works correctly by running the command below:

$ sudo ./perfq_app -b 0000:08:00.0 -o

Note: Here the -b option should be provided with the correct BDF of the FPGA endpoint card in the system. It can be checked using the lspci command. If successful, the application displays a Pass status as shown in the image below:

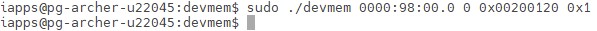

- The design example can be reset using the utility below when needed:

- Build the devmem utility.

$ cd software/user/cli/devmem $ make clean all

- Perform a reset by running the command below:

$ sudo ./devmem 0000:01:00.0 0 0x00200120 0x1

The expected printout is as shown below:

- Build the devmem utility.