A newer version of this document is available. Customers should click here to go to the newest version.

1. Overview

2. Quick Start Guide

3. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

4. Integrating the IP With Your Application

5. Simulating the IP

6. Validating the IP

A. Appendix A: Functional Description

B. Appendix B: Registers

C. Document Revision History for the GTS AXI Multichannel DMA IP for PCI Express*

2.1.1. Downloading and Installing Quartus® Prime Software

2.1.2. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

2.1.3. Configuring and Generating the GTS AXI Streaming Intel FPGA IP for PCI Express

2.1.4. Configuring and Generating the GTS System PLL Clocks Intel FPGA IP

2.1.5. Configuring and Generating the GTS Reset Sequencer Intel FPGA IP

2.1.6. Configuring and Generating the Reset Release IP

2.1.7. Instantiating and Connecting the IP Interfaces

2.1.8. Simulate, Compile and Validate the Design on Hardware

4.4.1. PCIe AXI-Stream TX Interface (ss_tx_st)

4.4.2. PCIe AXI-Stream RX Interface (ss_rx_st)

4.4.3. Control and Status Register Interface (ss_csr_lite)

4.4.4. Transmit Flow Control Credit Interface (ss_txcrdt)

4.4.5. Configuration Intercept Interface (CII)

4.4.6. Completion Timeout Interface (ss_cplto)

4.4.7. Function Level Reset (FLR) Interface

4.4.8. Control Shadow Interface (ss_ctrlshadow)

4.4.9. Error Interface

4.5.1. H2D AXI-Stream Manager (h2d_st_initatr)

4.5.2. D2H AXI-Stream Subordinate (d2h_st_respndr)

4.5.3. H2D/D2H AXI-MM Manager (dma_mm_initatr)

4.5.4. BAM AXI-MM Manager (bam_mm_initatr)

4.5.5. BAS AXI-MM Subordinate (bas_mm_respndr)

4.5.6. PIO AXI-Lite Manager (pio_lite_initiatr)

4.5.7. HIP Reconfiguration AXI-Lite Subordinate (user_csr_lite)

4.5.8. User Event MSI-X (user_msix)

4.5.9. User Event MSI (user_msi)

4.5.10. User Function Level Reset (user_flr)

4.5.11. User Configuration Intercept Interface

4.5.12. Configuration Slave (cs_lite_respndr)

A.1.1.1. H2D Data Mover

A.1.1.2. D2H Data Mover

A.1.1.3. Descriptors

A.1.1.4. AXI4-Lite PIO Manager

A.1.1.5. AXI-MM Write (H2D) and Read (D2H) Manager

A.1.1.6. AXI-Stream Manager (H2D) and Subordinate (D2H)

A.1.1.7. User MSI-X

A.1.1.8. User Function Level Reset (FLR)

A.1.1.9. Control and Status Registers

3.2.2.1.3. Bursting Slave Mode

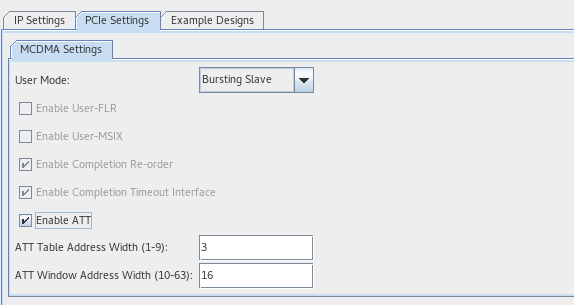

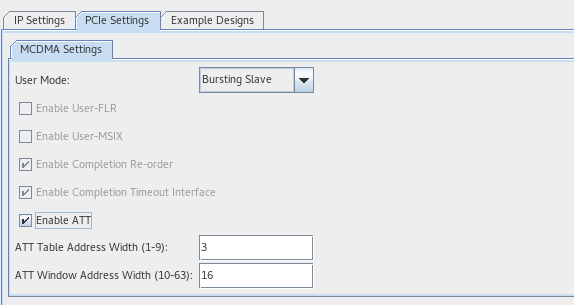

Figure 11. Root Port Bursting Slave Parameters

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Enable Completion Reorder | On | On | Enables completion reorder. |

| Enable Completion Timeout Interface | On | On | Enables the completion timeout interface. |

| Enable ATT | On/Off | Off | Enables the Address Translation Table for BAS. |

| ATT Table Address Width | 1 - 9 | 3 | Sets the depth of ATT. The depth is equal to 2 to the power of the number entered. |

| ATT Window Address Width | 10 - 63 | 16 | Sets the number of BAS address bits to be used directly. |

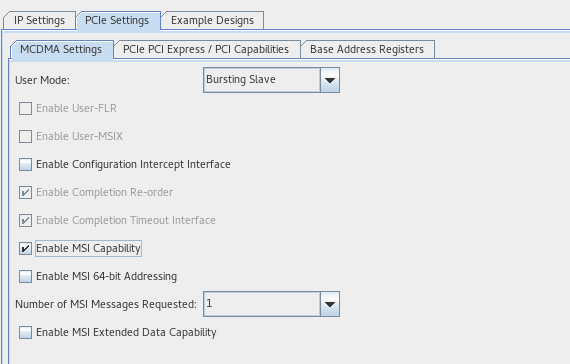

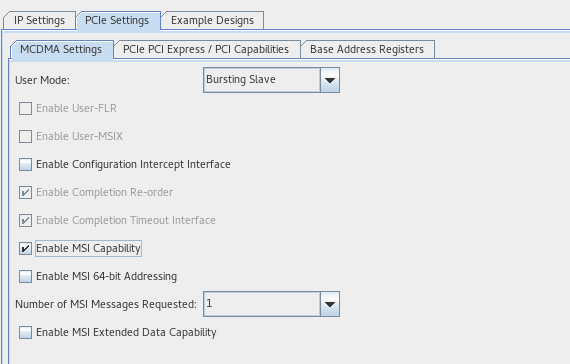

Figure 12. Endpoint Bursting Slave Parameters

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Enable Configuration Intercept Interface | On/Off | Off | Select to enable the user application to detect the occurrence of a CFG request on the link and to modify its behavior via the configuration intercept interface. Applicable to Endpoint only. |

| Enable Completion Reorder | On | On | Enables completion reorder. |

| Enable Completion Timeout Interface | On | On | Enables the completion timeout interface. |

| Enable MSI Capability | On/Off | Off | Enables or disables the MSI capability.

Note: MSI is supported only in BAS and BAM + BAS modes.

|

| Enable MSI 64-bit Addressing | On/Off | Off | Enables or disables 64-bit MSI addressing. |

| Number of MSI Messages Requested | 1, 2, 4, 8, 16, 32 | 1 | Sets the number of messages that the application can request in the multiple message capable field of the Message Control register. |

| Enable MSI Extended Data Capability | On/Off | Off | Enables or disables MSI extended data capability. |