A newer version of this document is available. Customers should click here to go to the newest version.

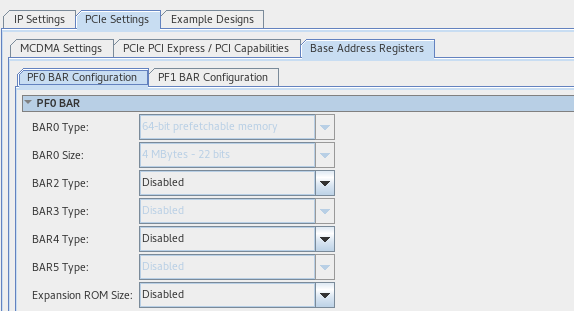

3.2.2.3. Base Address Registers

The Base Address Registers settings are available for the Native Endpoint design. In Multichannel DMA, BAM+MCDMA and BAM+BAS+MCDMA modes, BAR0 is allocated to access a 4 MB space that internal IP registers are mapped to.

In Multichannel DMA mode, BAR2 size can be configured through the BAR2 Address Width parameter in MCDMA Settings.

Supported BAR types for the user application are as follows (vary by user mode):

- BAR 0/2/4: Disabled, 64-bit prefetchable memory, 64-bit non-prefetchable memory.

- BAR 1/3/5: Disabled.

If you select a 64-bit type for BAR 0/2/4, then the adjacent BAR 1/3/5 is disabled.

The following tables show the BAR and Expansion ROM parameters that can be configured in each user mode.

| PF0 BAR | Multichannel DMA | Bursting Master | Bursting Slave |

|---|---|---|---|

| BAR0 | 64-bit prefetchable memory Size: 4 MB - 22 bits Note: BAR not available to user application. |

Y | Y |

| BAR1 | Disabled Note: BAR not available to user application. |

Disabled | Disabled |

| BAR2 | 64-bit prefetchable memory Size: 4 MB - 22 bits Note: BAR not available to user application. |

Y | Y |

| BAR3 | Disabled Note: BAR not available to user application. |

Disabled | Disabled |

| BAR4 | Disabled Note: BAR not available to user application. |

Y | Y |

| BAR5 | Disabled Note: BAR not available to user application. |

Disabled | Disabled |

| Expansion ROM | Y | Y | Y |

| PF0 BAR | BAM+BAS | BAM+MCDMA | BAM+BAS+MCDMA |

|---|---|---|---|

| BAR0 | Y | 64-bit prefetchable memory Size: 4 MB - 22 bits

Note: BAR not available to user application.

|

64-bit prefetchable memory Size: 4 MB - 22 bits

Note: BAR not available to user application.

|

| BAR1 | Disabled |

Disabled

Note: BAR not available to user application.

|

Disabled

Note: BAR not available to user application.

|

| BAR2 | Y | Y | Y |

| BAR3 | Disabled |

Disabled | Disabled |

| BAR4 | Y | Y | Y |

| BAR5 | Disabled |

Disabled | Disabled |

| Expansion ROM | Y | Y | Y |