A newer version of this document is available. Customers should click here to go to the newest version.

1. Overview

2. Quick Start Guide

3. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

4. Integrating the IP With Your Application

5. Simulating the IP

6. Validating the IP

A. Appendix A: Functional Description

B. Appendix B: Registers

C. Document Revision History for the GTS AXI Multichannel DMA IP for PCI Express*

2.1.1. Downloading and Installing Quartus® Prime Software

2.1.2. Configuring and Generating the GTS AXI Multichannel DMA IP for PCI Express

2.1.3. Configuring and Generating the GTS AXI Streaming Intel FPGA IP for PCI Express

2.1.4. Configuring and Generating the GTS System PLL Clocks Intel FPGA IP

2.1.5. Configuring and Generating the GTS Reset Sequencer Intel FPGA IP

2.1.6. Configuring and Generating the Reset Release IP

2.1.7. Instantiating and Connecting the IP Interfaces

2.1.8. Simulate, Compile and Validate the Design on Hardware

4.4.1. PCIe AXI-Stream TX Interface (ss_tx_st)

4.4.2. PCIe AXI-Stream RX Interface (ss_rx_st)

4.4.3. Control and Status Register Interface (ss_csr_lite)

4.4.4. Transmit Flow Control Credit Interface (ss_txcrdt)

4.4.5. Configuration Intercept Interface (CII)

4.4.6. Completion Timeout Interface (ss_cplto)

4.4.7. Function Level Reset (FLR) Interface

4.4.8. Control Shadow Interface (ss_ctrlshadow)

4.4.9. Error Interface

4.5.1. H2D AXI-Stream Manager (h2d_st_initatr)

4.5.2. D2H AXI-Stream Subordinate (d2h_st_respndr)

4.5.3. H2D/D2H AXI-MM Manager (dma_mm_initatr)

4.5.4. BAM AXI-MM Manager (bam_mm_initatr)

4.5.5. BAS AXI-MM Subordinate (bas_mm_respndr)

4.5.6. PIO AXI-Lite Manager (pio_lite_initiatr)

4.5.7. HIP Reconfiguration AXI-Lite Subordinate (user_csr_lite)

4.5.8. User Event MSI-X (user_msix)

4.5.9. User Event MSI (user_msi)

4.5.10. User Function Level Reset (user_flr)

4.5.11. User Configuration Intercept Interface

4.5.12. Configuration Slave (cs_lite_respndr)

A.1.1.1. H2D Data Mover

A.1.1.2. D2H Data Mover

A.1.1.3. Descriptors

A.1.1.4. AXI4-Lite PIO Manager

A.1.1.5. AXI-MM Write (H2D) and Read (D2H) Manager

A.1.1.6. AXI-Stream Manager (H2D) and Subordinate (D2H)

A.1.1.7. User MSI-X

A.1.1.8. User Function Level Reset (FLR)

A.1.1.9. Control and Status Registers

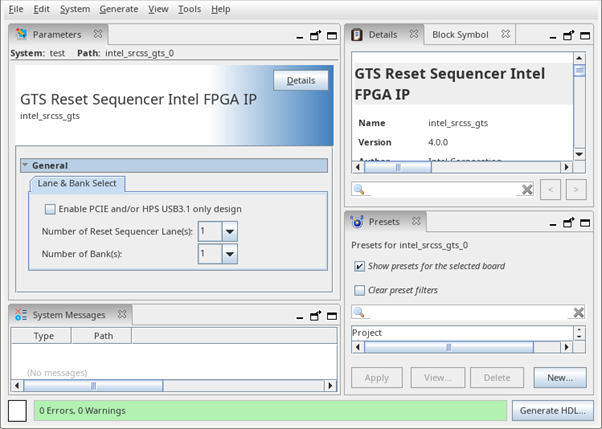

2.1.5. Configuring and Generating the GTS Reset Sequencer Intel FPGA IP

Following is the process to configure and generate the GTS Reset Sequencer Intel FPGA IP. You have to instantiate only one GTS Reset Sequencer Intel FPGA IP for all the PCIe and non-PCIe channels on a side of the device.

- Select GTS Reset Sequencer Intel FPGA IP in the IP Catalog.

- Select GTS Reset Sequencer Intel FPGA IP (Library → Interface Protocols → Transceiver PHY → GTS Reset Sequencer Intel FPGA IP) and then click Add.

- Specify a top-level name for your new custom IP variation and the directory for it. The IP Parameter Editor saves the IP variation settings in a file named <your_ip>.ip.

- Click Create. The IP Parameter Editor appears as shown in the figure below.

- Set the number of banks and lanes.

- If the design only has PCIe channels on a side of the device, select the Enable PCIE and/or HPS USB3.1 only design option.

- Set the Number of Reset Sequencer Lane(s) based on the total number of non-PCIe channels on the side of the device used in the design. The number of PCIe channels are not counted in the Number of Reset Sequencer Lane(s) parameter.

- For a PCIe x8 design, set Number of Bank(s) to 2. For x4/x2/x1 designs, set Number of Bank(s) to 1.

- Generate the GTS System PLL Clocks Intel FPGA IP.

- Click Generate HDL. The Generation dialogue box appears. Specify the output file generation options.

- Click Generate. The IP variation files are generated according to your specifications.

- Click Close when the IP generation is complete. The IP Parameter Editor adds the top-level.ip file to the current project automatically. If you are prompted to manually add the .ip file to the project, click Project → Add/Remove Files in Project to add the file.

Note: For more descriptions of how to connect the GTS Reset Sequencer Intel FPGA IP, refer to Implementing the GTS Reset Sequencer Intel FPGA IP.

Related Information